## VUS 1/1 VU0000001

-

FOOTSCRAY INSTITUTE OF TECHNOLOGY LIBRARY CALL NO.

629.895 COT

NOT FOR LOAN

۲

ACC'N NO.

XX

## THE APPLICATION OF MICROCOMPUTERS

IN

# (DISTRIBUTED MICROCOMPUTERS)

A Thesis submitted for Examination for the Degree of Master of Engineering

by

Alan. W. Cotton.

Dip. E.E., Dip. Electronic Eng., B. Elec. Eng. (V.I.C.)

#### DEPARTMENT

#### OF

## ELECTRICAL AND ELECTRONIC ENGINEERING, FOOTSCRAY INSTITUTE OF TECHNOLOGY.

#### SYNOPSIS

This thesis is concerned with the study of Microcomputers in Large Industrial Installations as a replacement for the traditional remote control and monitoring techniques.

A typical conveyor transport installation is described and was used as the basis for the system model developed by the author.

The thesis outlines the traditional techniques of control and data transmission in a widely distributed conveyor network and shows how they were used, or modified, for a microcomputer-based scheme.

In addition to the method of data transmission adopted by the author for the system model, the need for standard data transmission techniques (including error checking) is also described.

To be complete, research into distributed microcomputer systems must cover computer techniques (software and hardware), input/output requirements and linking techniques. The thesis describes each facet in detail, and includes the problems encountered during implementation.

The thesis also includes an outline of the Loy Yang project which is one of two systems for the State Electricity Commission of Victoria (SECV) where some of the concepts have been implemented since the research was completed.

(i)

ACKNOWLEDGEMENTS

Acknowledgement is gratefully extended to Messrs W A Evans and G J Lowe, to the Footscray Institute of Technology and to the State Electricity Commission of Victoria for providing the opportunity and financial assistance to carry out this research project.

The project was supervised by Messrs W A Evans and G J Lowe, for whose advice I am grateful.

There are many people I wish to thank, in particular the following:

My wife - for her patience throughout the work.

•

Messrs J M Alexander, H R Bunting and E J P Clayfield - for their guidance, continued support and encouragement.

Messrs H W Bloxom and R M Glenn - for the original motivations behind the research.

Messrs J Ikin, D Marshall and R Said - for their assistance in the compilation of this thesis.

Messrs I Strachan, D Jagmin, L Omachen, G Atkinson, D Wilson and T Stork - for their assistance.

Miss E C Watson, Mrs L Price and Mrs H Langley for the organising and the typing of the thesis.

(ii)

#### STATEMENT OF ORIGINALITY

I certify that the work reported in this thesis is my own in the following respects:

- (a) The writing of this thesis is my own work.

- (b) The design and implementation of the distributed control system, writing and testing of software, and the development of the electronic circuitry are my own work.

No part of this work has been presented by the author for any other Degree. The author's publication relating to the topic is listed below and a reprint is included in Appendix E.

> LOWE, G J, and COTTON, A W, "Hierarchical Control Using Satellite Microprocessors" Conference on Microprocessor Systems, The Institution of Engineers, Australia, 15-16 November, 1977.

•

Alan W Cotton

#### TABLE OF CONTENTS

| SYNOF | PSIS      |                                                       | (i)         |  |  |

|-------|-----------|-------------------------------------------------------|-------------|--|--|

| ACKNO | DWLEDGEME | ENTS                                                  | (ii)        |  |  |

| STATE | EMENT OF  | ORIGINALITY                                           | (iii)       |  |  |

| 1     | INTRO     | INTRODUCTION                                          |             |  |  |

|       | 1.1       | BACKGROUND                                            | 1           |  |  |

|       |           | 1.1.1 General                                         | 1           |  |  |

|       |           | 1.1.2 The Process Under Investigation                 | 2           |  |  |

|       |           | 1.1.3 Developments in Open Cut Control                | 3           |  |  |

|       | 1.2       | OBJECTIVES OF THE RESEARCH                            | 5           |  |  |

| 2     | LITER     | RATURE REVIEW                                         | 8           |  |  |

|       | 2.1       | TRADITIONAL TECHNIQUES OF OPEN CUT CONTRO             | L 8         |  |  |

|       | 2.2       | MICROCOMPUTER HISTORY                                 | 11          |  |  |

|       | 2.3       | MONITORING AND CONTROL DEVELOPMENTS                   | 12          |  |  |

| 3     | THE F     | RESEARCH PROGRAM                                      | 15          |  |  |

|       | 3.1       | DETERMINATION OF THE SUITABILITY                      |             |  |  |

|       |           | OF MICROCOMPUTER SUB-SYSTEMS                          | 15          |  |  |

|       |           | 3.1.1 General                                         | 15          |  |  |

|       |           | 3.1.2 A Single/Multiple Microprocessor-<br>Sub-system | based<br>19 |  |  |

|       |         |              | A Single Microprocessor-based<br>Microcomputer Sub-system | 19          |

|-------|---------|--------------|-----------------------------------------------------------|-------------|

|       |         |              | A Multiple Microprocessor<br>Microcomputer Sub-system     | 20          |

|       | 3.1.3   |              | and Disadvantages of<br>ter-based Systems                 | 21          |

| 3.2   | ESTABL  | SHMENT OF T  | HE HIERARCHY OF THE                                       |             |

|       | PROTOTY | PE SYSTEM    |                                                           | 24          |

|       | 3.2.1   | General      |                                                           | 24          |

|       | 3.2.2   | Master Sub   | -system                                                   | 28          |

|       | 3.2.3   | Sub-master   | Sub-system (Front-end)                                    | 31          |

|       | 3.2.4   | Slave Sub-   | systems                                                   | 33          |

|       | 3.2.5   | Methods of   | Communication                                             | 35          |

|       |         | 3.2.5.1      | Party-line                                                | 35          |

|       |         | 3.2.5.2      | Radial                                                    | 36          |

| 3.3   | INVEST  | IGATION OF T | HE DATA TRANSFER                                          |             |

|       | TECHNI  | QUES FOR THE | MODEL                                                     | 36          |

|       | 3.3.1   | Modes of O   | peration                                                  | 36          |

|       |         | 3.3.1.1      | Interrupt Operation                                       | <b>37</b> , |

|       |         | 3.3.1.2      | Polling Operation                                         | 37          |

|       | 3.3.2   | The Messag   | e Protocol of the Model                                   | 38          |

|       | 3.3.3   | Error Dete   | ction in the Model                                        | 43          |

| THE E | XPERIME | NTAL MODEL   |                                                           | 44          |

| 4.1   | DEVELO  | MENT OF THE  | MODEL                                                     | 44          |

| 4.2   | THE HAP | NDWARE REQUI | REMENTS OF THE MODEL                                      | 48          |

|       | 4.2.1   | Master Com   | puter                                                     | 48          |

|       | 4.2.2   | Front-end    | Computer                                                  | 50          |

|       | 4.2.3   | Slave Comp   | uter                                                      | 54          |

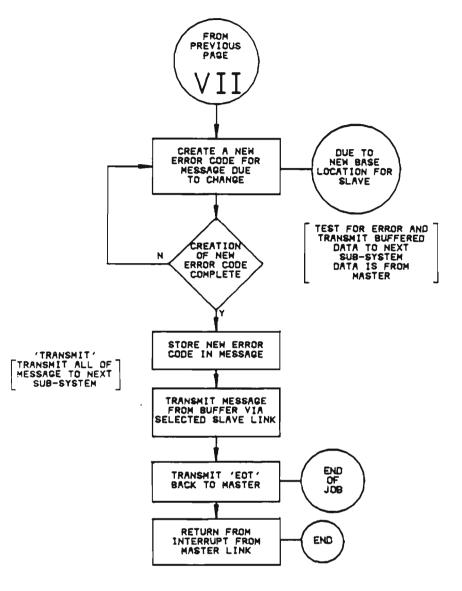

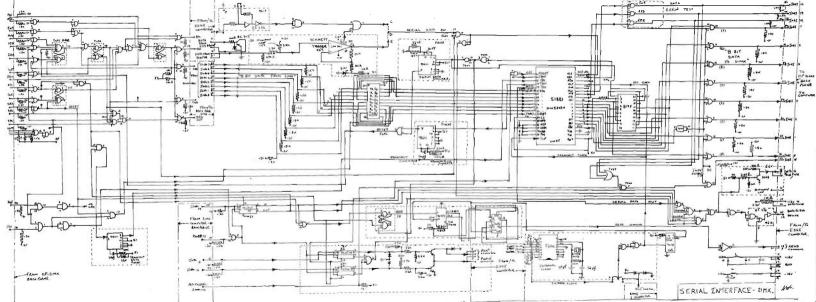

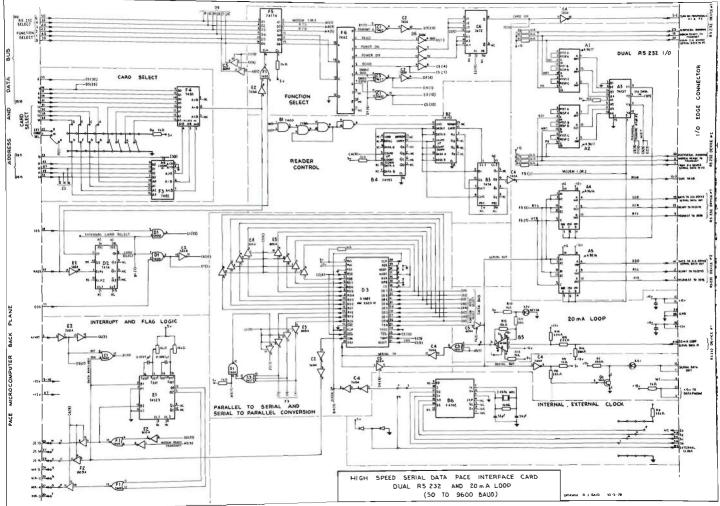

|       | 4.2.4   | High Speed   | Data Interfaces                                           | 56          |

|                                               |         | 4.2.4.1               | General                                   | 56  |

|-----------------------------------------------|---------|-----------------------|-------------------------------------------|-----|

|                                               |         | 4.2.4.2               | The Basic Building Blocks                 | 58  |

|                                               |         | 4.2.4.3               | The High Speed Data Link of<br>the Master | 60  |

|                                               |         | 4.2.4.4               | The High Speed Data Links                 | 68  |

|                                               |         |                       | of the front-end and the slaves           |     |

|                                               | 4.2.5   | The Data              | Transfer Paths                            | 73  |

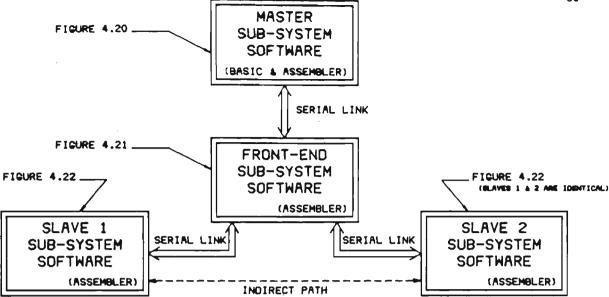

| 4.3                                           | THE SYS | TEM SOFTWA            | RE FOR THE MODEL                          | 75  |

|                                               | 4.3.1   | General               |                                           | 75  |

|                                               | 4.3.2   | System So             | ftware Elements                           | 78  |

|                                               |         | 4.3.2.1               | Standard Software                         | 78  |

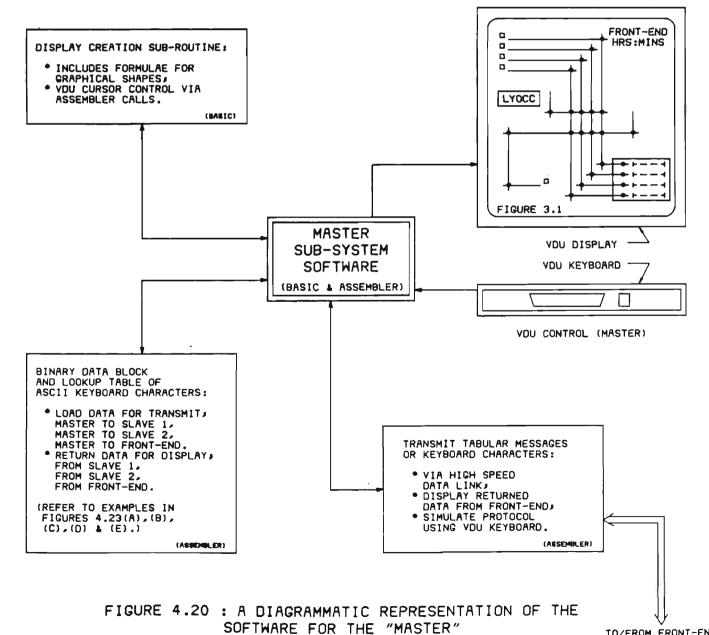

|                                               |         | 4.3.2.2               | Developed Software<br>for the Master      | 79  |

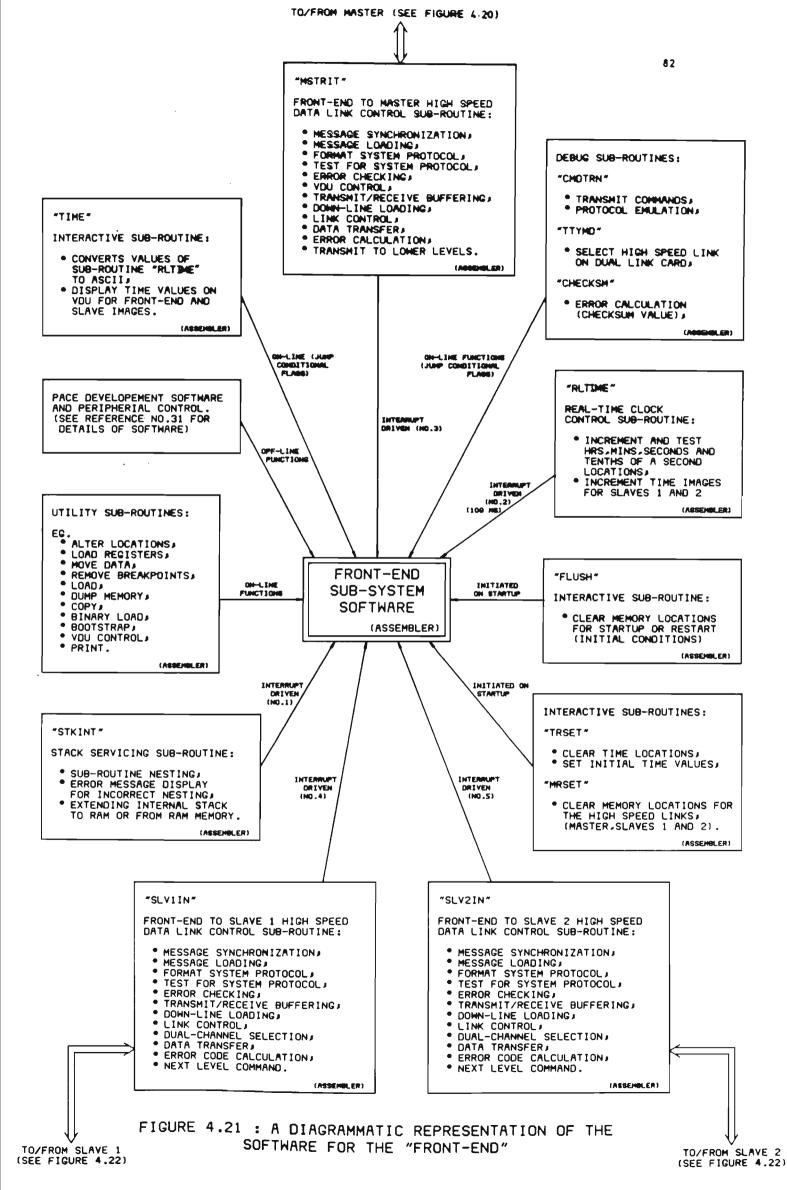

|                                               |         | 4.3.2.3               | Developed Software for the front-end      | 81  |

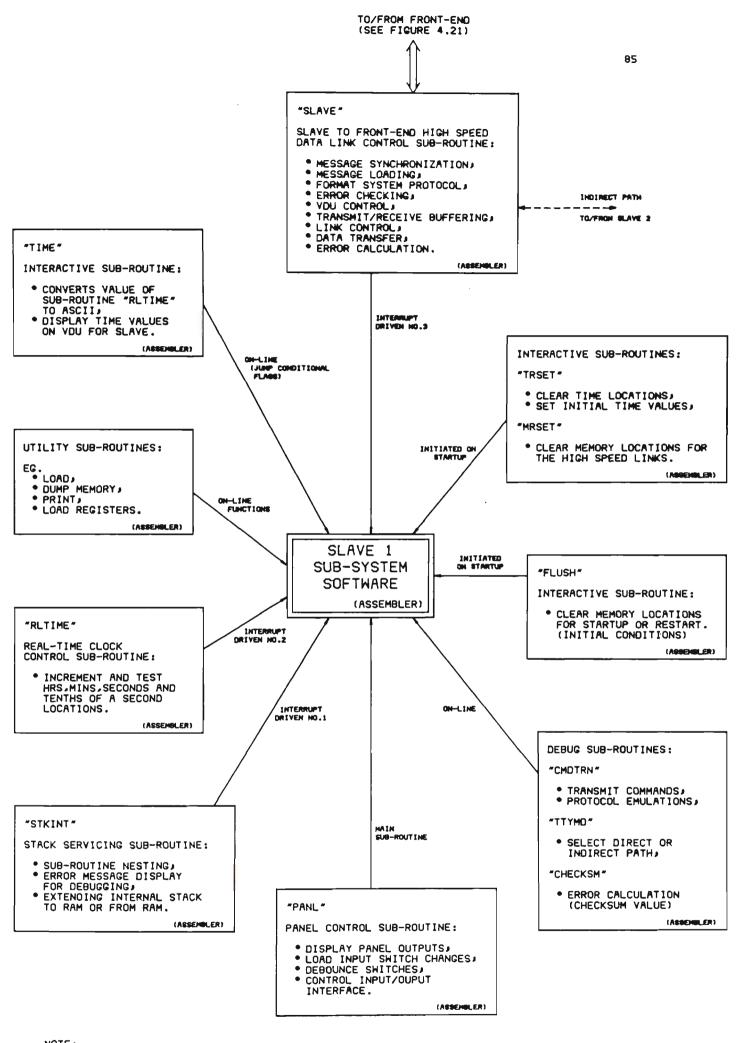

|                                               |         | 4.3.2.4               | Developed Software for the<br>Slaves      | 83  |

|                                               | 4.3.3   | The Struc<br>Software | ture of the Fundamental                   | 86  |

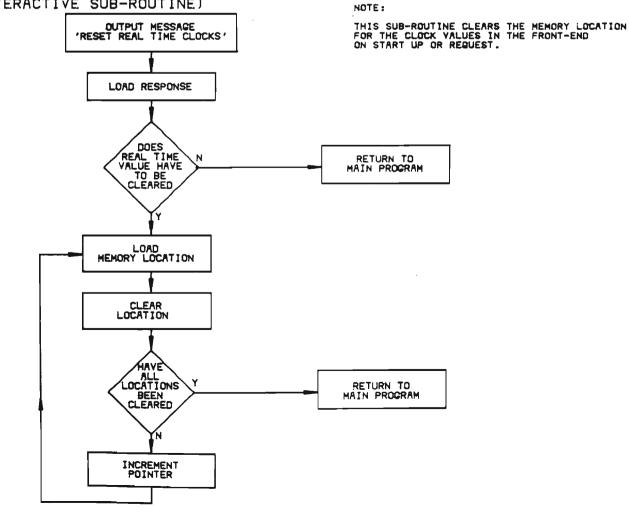

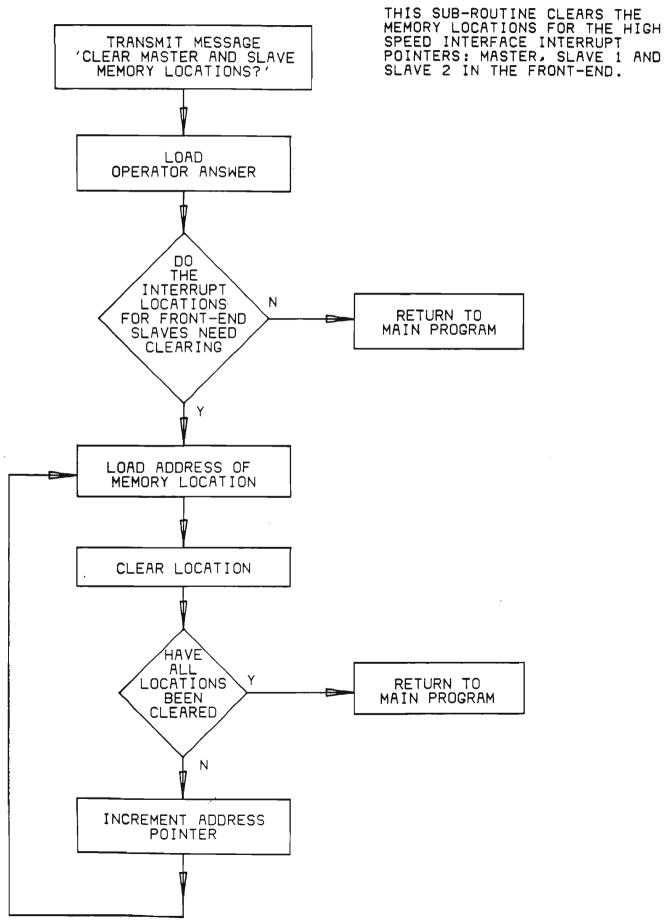

|                                               |         | 4.3.3.1               | Interactive Programs                      | 86  |

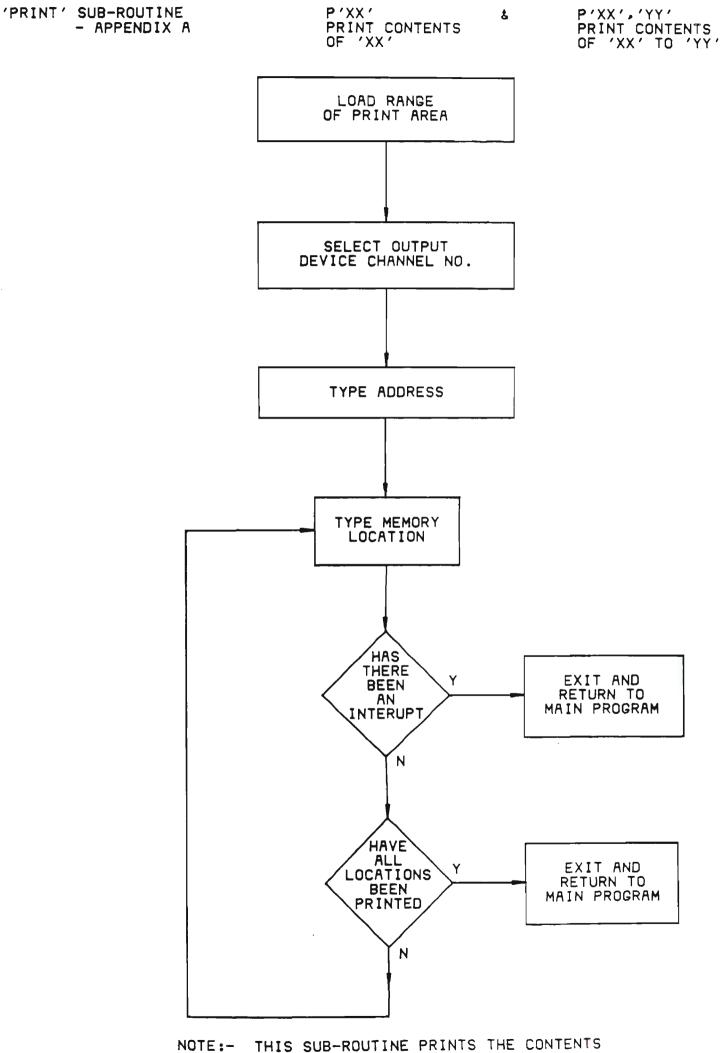

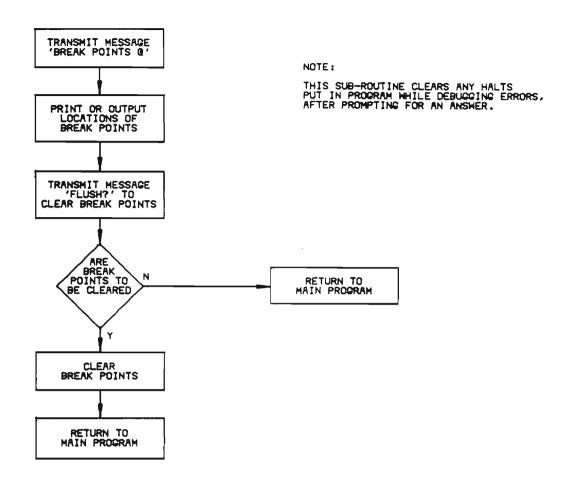

|                                               |         | 4.3.3.2               | The Debug Programs                        | 87  |

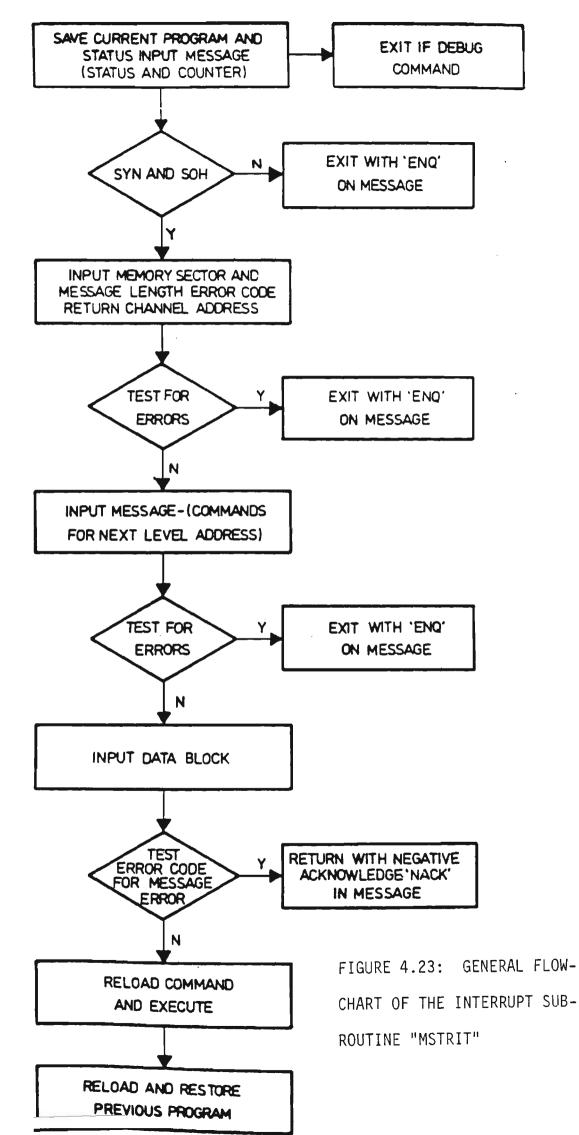

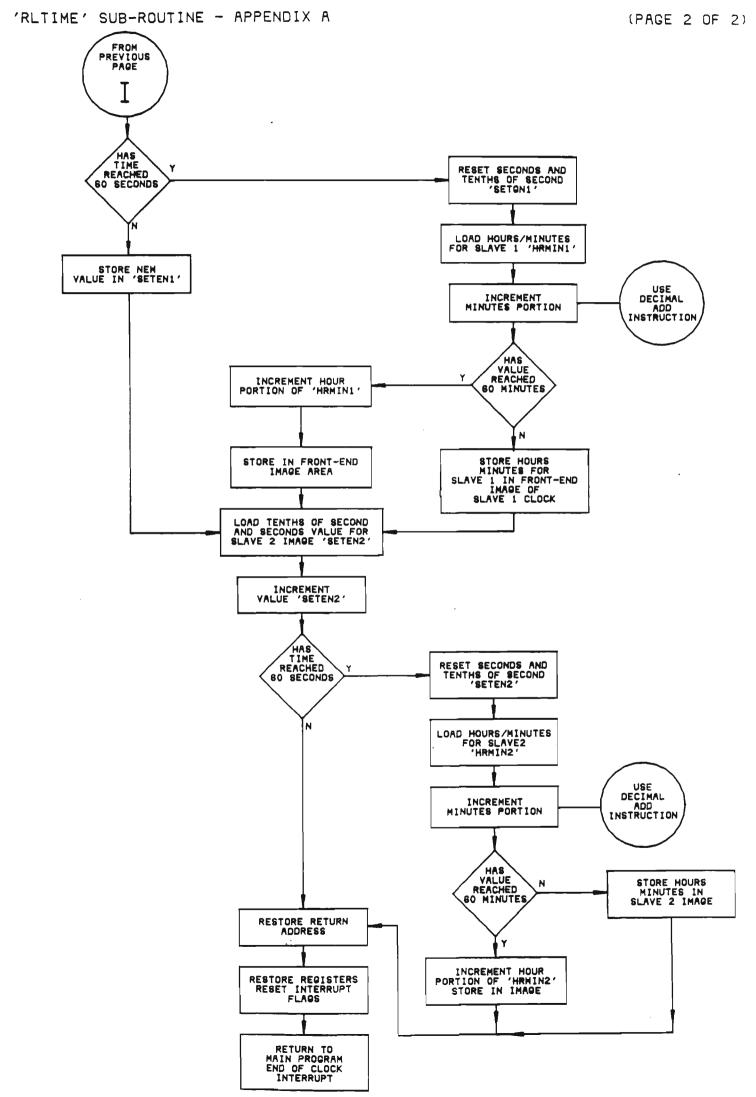

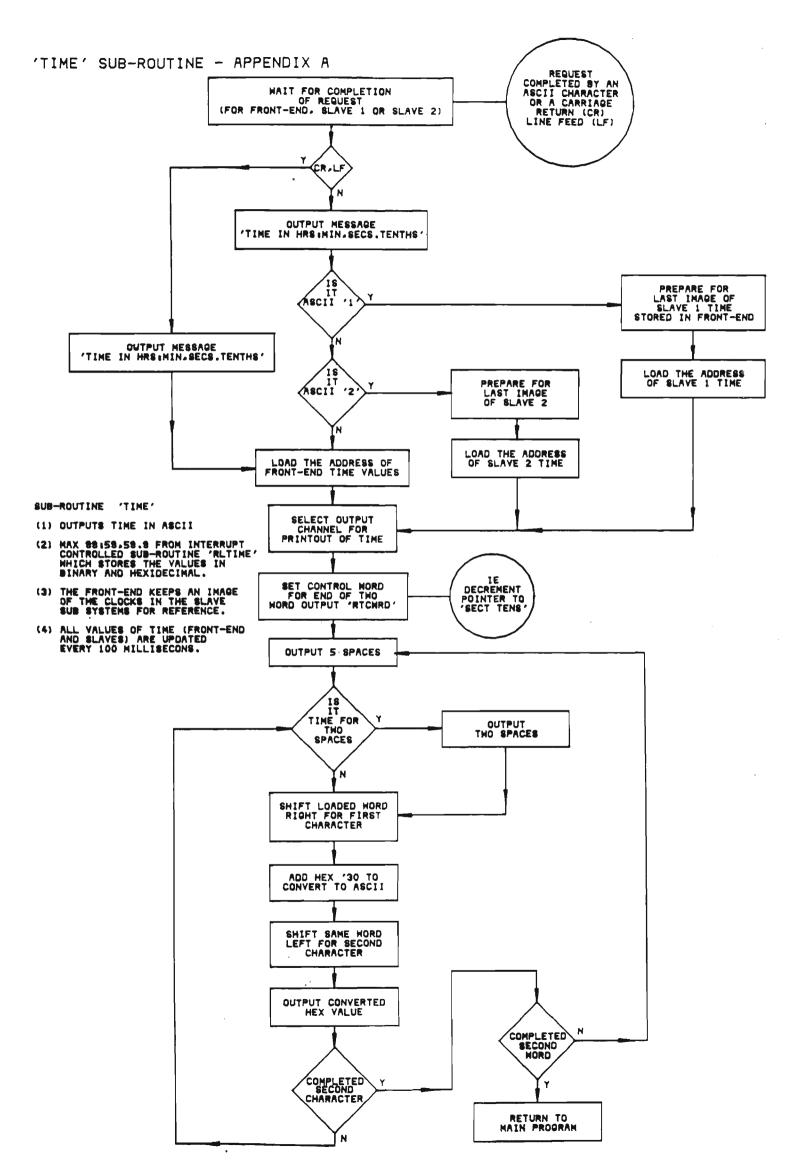

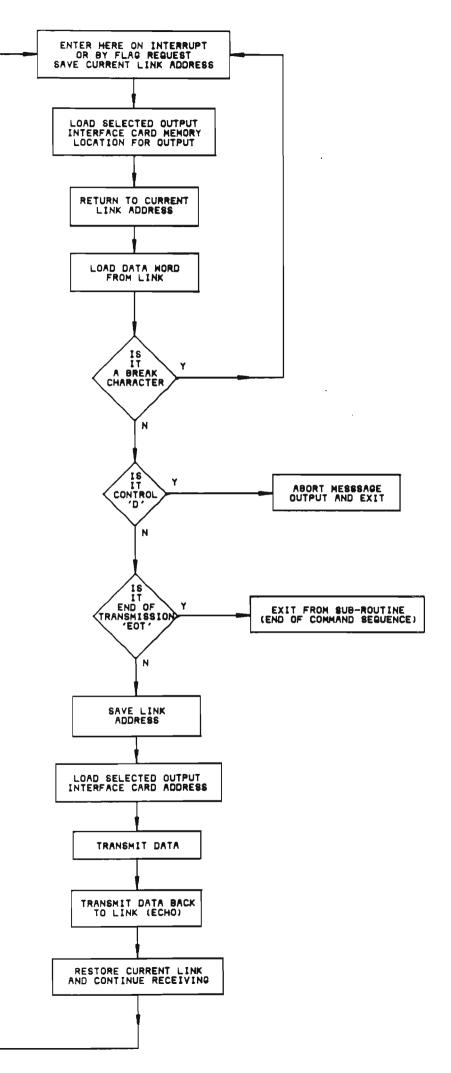

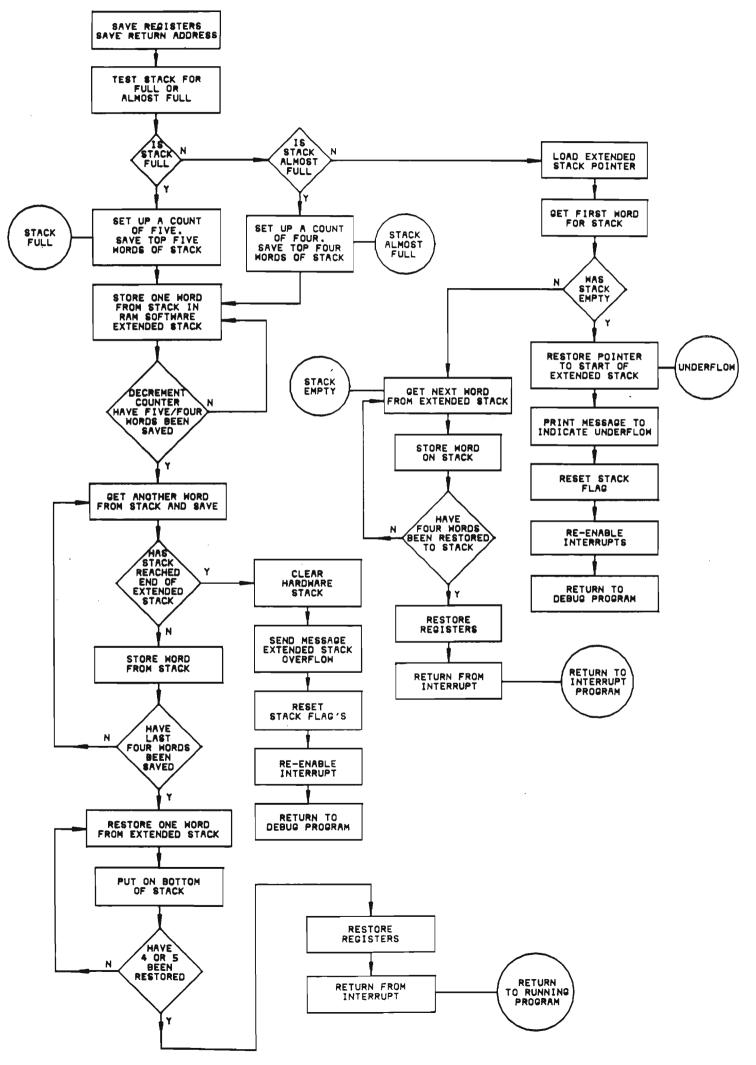

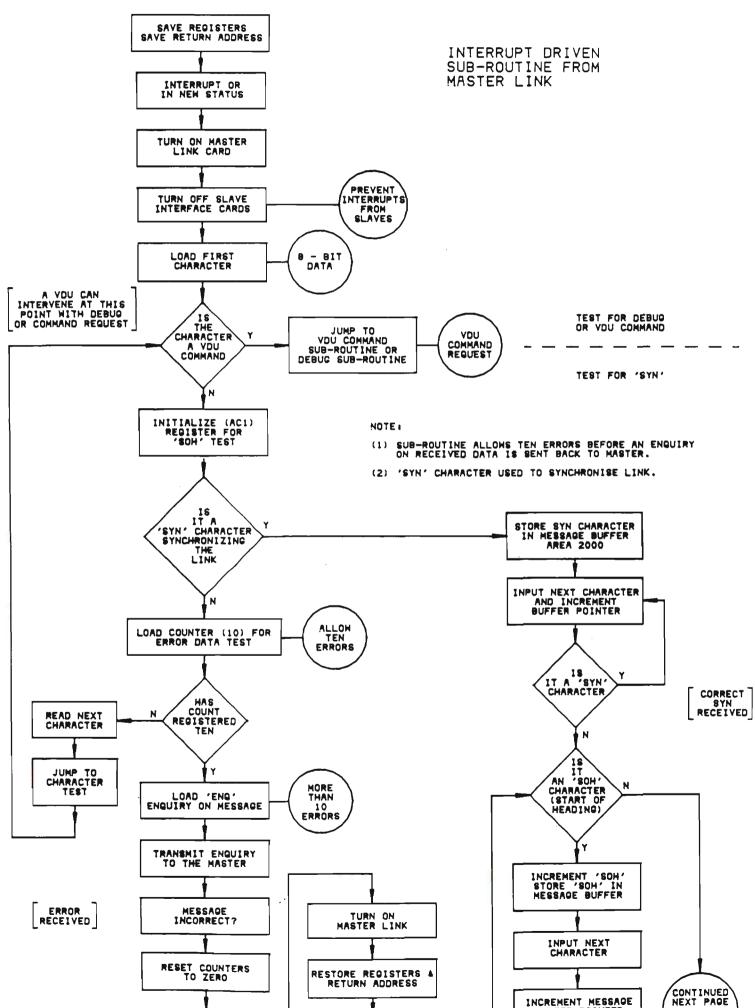

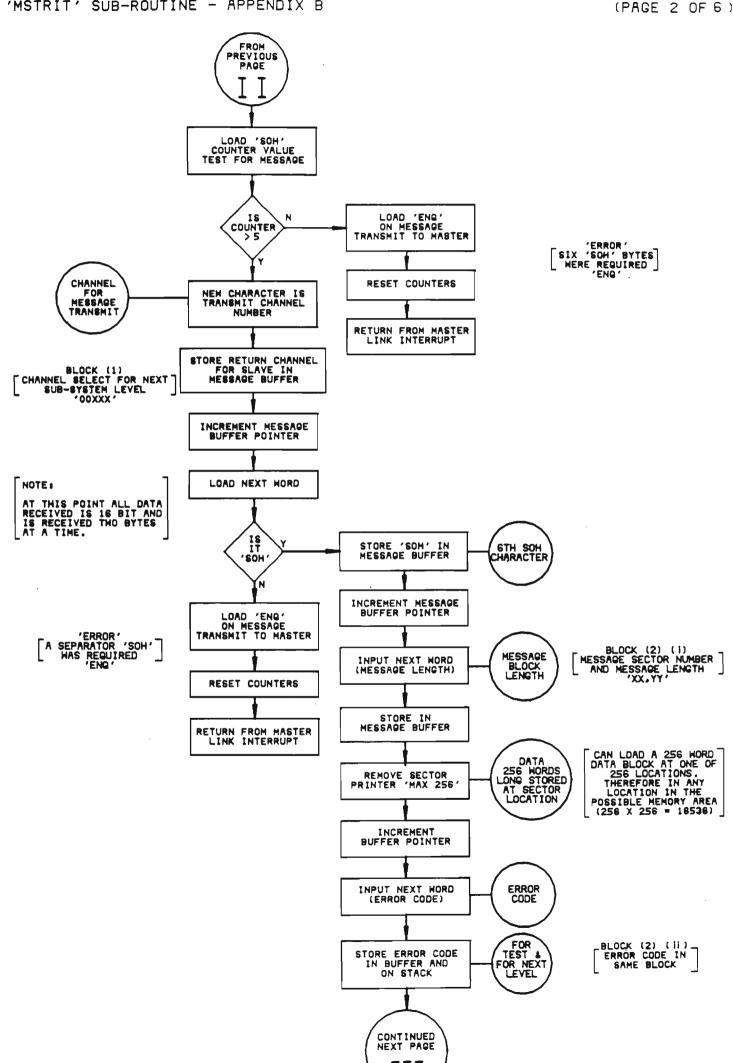

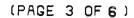

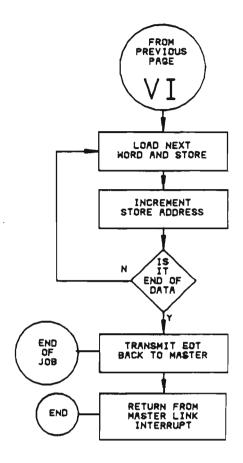

|                                               |         | 4.3.3.3               | The Interrupt Sub-routines                | 89  |

|                                               |         | 4.3.3.4               | BASIC Sub-routines                        | 98  |

|                                               | 4.3.4   | The Opera             | ting Strategy of the Model                | 99  |

|                                               |         |                       |                                           |     |

| THE VALIDATION OF THE CONCEPTS INVESTIGATED 1 |         |                       |                                           |     |

| 5.1                                           | THE PER | FORMANCE O            | F THE SYSTEM MODEL                        | 104 |

|                                               | 5.1.1   | Independer            | nt Control                                | 104 |

|                                               |         |                       |                                           |     |

5.1.2 Results of Actual Data Transmission 105

5

PAGE

PAGE

|            |       | 5.1.3                                                       | Performan<br>Manufactu |       |                     | rdware to the<br>ications | 9     | 107 |

|------------|-------|-------------------------------------------------------------|------------------------|-------|---------------------|---------------------------|-------|-----|

|            |       | 5.1.4                                                       | Software               | Perfo | rmance              |                           |       | 108 |

|            |       | 5.1.5                                                       | Increased              | Relia | ability             |                           |       | 108 |

|            |       | 5.1.6                                                       | Interrupt              | Serv  | icing fo            | or Multiple               | Tasks | 111 |

|            | 5.2   | THE SUCCESSFUL IMPLEMENTATION IN AN OPEN CUT<br>ENVIRONMENT |                        |       |                     |                           | CUT   | 111 |

|            |       | 5.2.1                                                       | General                |       |                     |                           |       | 111 |

|            |       | 5.2.2                                                       | The Loy Y              | ang S | ystem               |                           |       | 111 |

|            |       |                                                             | 5.2.2.1                | The   | Central             | Computer Sy               | stem  | 112 |

|            |       |                                                             | 5.2.2.2                |       | Data Aco<br>pment   | quisition                 |       | 113 |

|            |       |                                                             | 5.2.2.3                |       | Microcom<br>rollers | nputer Conve              | yor   | 114 |

|            |       | 5.2.3                                                       | The Conce<br>Loy Yang  |       |                     | ated in the               |       | 114 |

| 6          | CONCL | USIONS                                                      |                        |       |                     |                           | £     | 116 |

| 7          | FURTH | ER WORK                                                     | AND RECOMM             | ENDAT | IONS                |                           |       | 119 |

| REFERENCES |       |                                                             |                        |       | 122                 |                           |       |     |

6

7

.

#### APPENDICES

#### PAGE

- APPENDIX B : SYSTEM SOFTWARE : PART B 153

- APPENDIX C : MASTER HIGH SPEED SERIAL DATA INTERFACE 172 CARD "A (50 TO 9600 BAUD) SERIAL INTERFACE TO THE HEWLETT PACKARD 21 MX MINICOMPUTER"

- APPENDIX D : FRONT-END AND SLAVE HIGH SPEED SERIAL 174 DATA INTERFACE CARD "A DUAL (50 TO 9600 BAUD) SERIAL INTERFACE TO NATIONAL SEMICONDUCTOR'S PACE MICROCOMPUTER"

- APPENDIX E : THE AUTHOR'S PUBLISHED PAPER 176 "HIERARCHICAL CONTROL USING SATELLITE MICROPROCESSORS" TECHNICAL CONFERENCE OF THE INSTITUTION OF ENGINEERS, AUSTRALIA

- APPENDIX F : INDUSTRY STANDARDS FOR MESSAGE 183

PROTOCOLS AND ERROR DETECTION

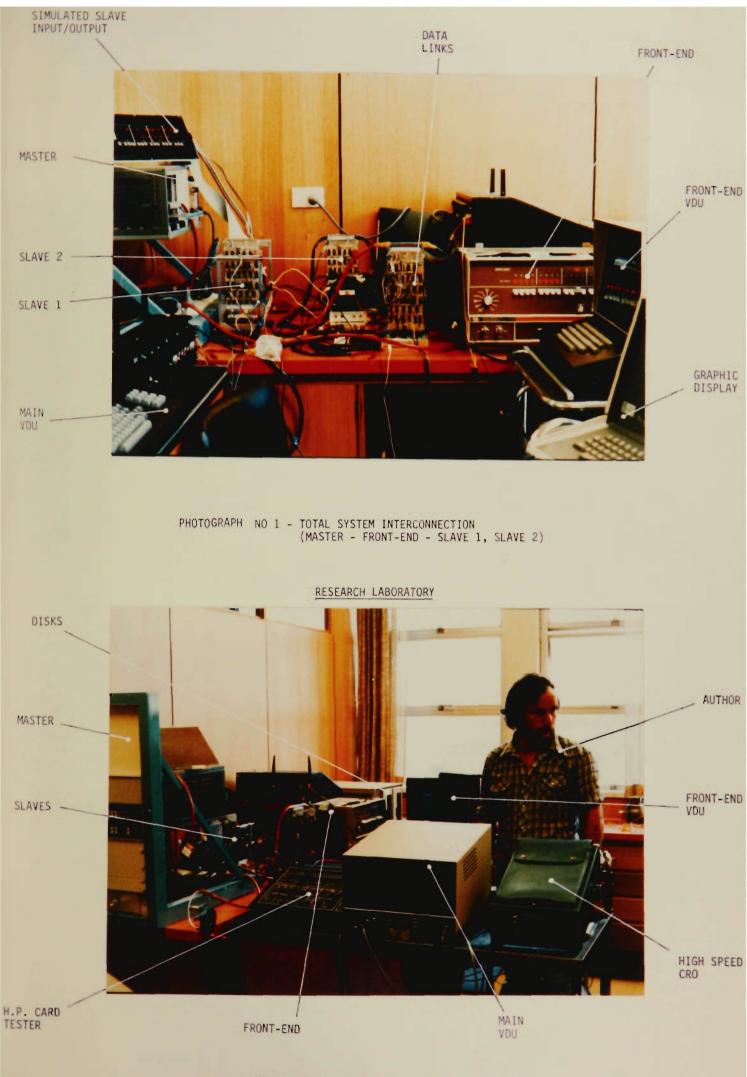

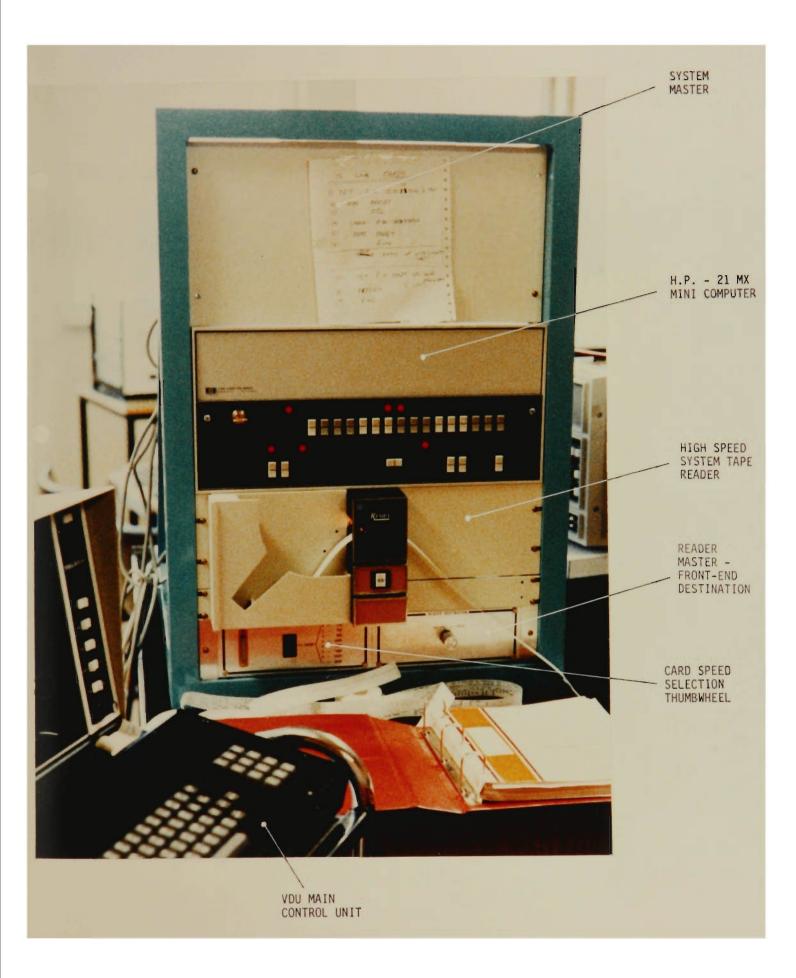

### PHOTOGRAPHS

| No | 1  | TOTAL SYSTEM INTERCONNECTION         | 25    |

|----|----|--------------------------------------|-------|

|    | 2  | SYSTEM LAYOUT                        | 25    |

|    | 3  | SYSTEM INTERCONNECTION ARRANGEMENT   | 51    |

|    | 4  | MASTER COMPUTER FRONT VIEW           | 29    |

|    | 5  | MASTER COMPUTER REAR VIEW            | 30    |

|    | 6  | SYSTEM INTERCONNECTION AND FRONT-END |       |

|    |    | ARRANGEMENT                          | 32    |

|    | 7  | FRONT-END AND SLAVES 1 AND 2 LAYOUT  | 32    |

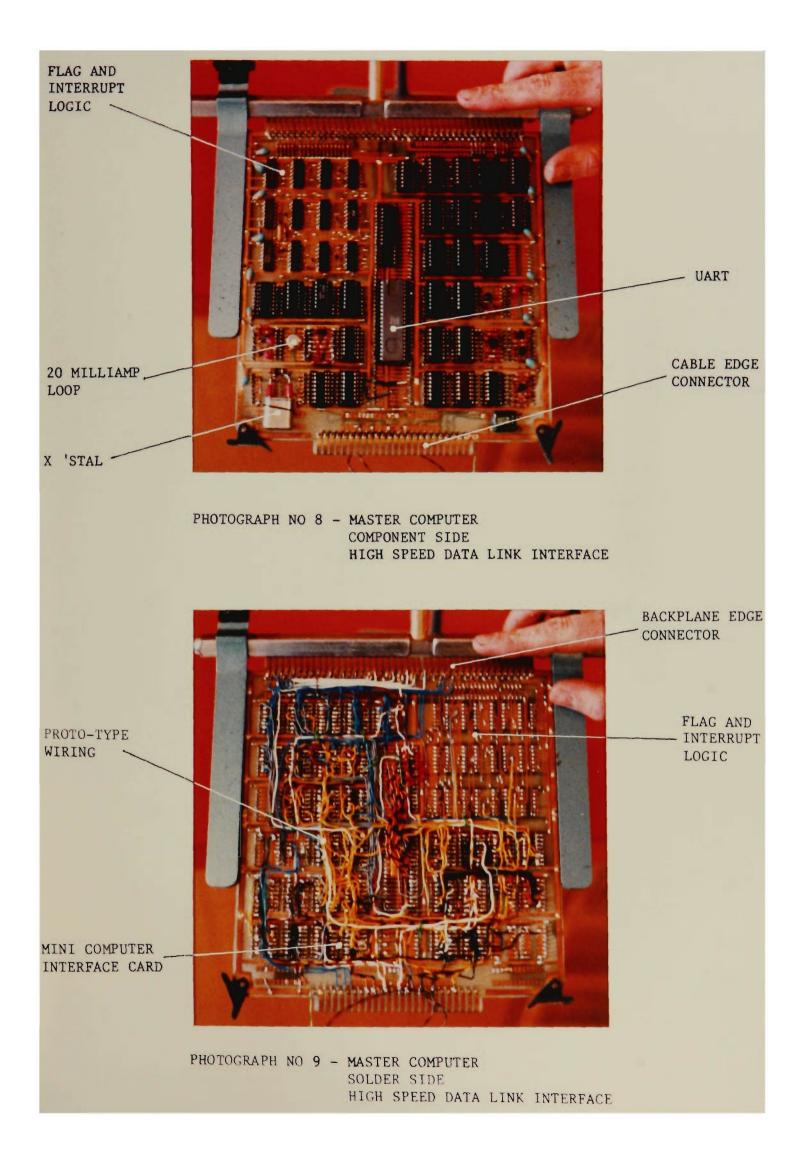

|    | 8  | MASTER COMPUTER INTERFACE            | 57(a) |

|    |    | . COMPONENT SIDE                     |       |

|    | 9  | MASTER COMPUTER INTERFACE            | 57(a) |

|    |    | . SOLDER SIDE                        |       |

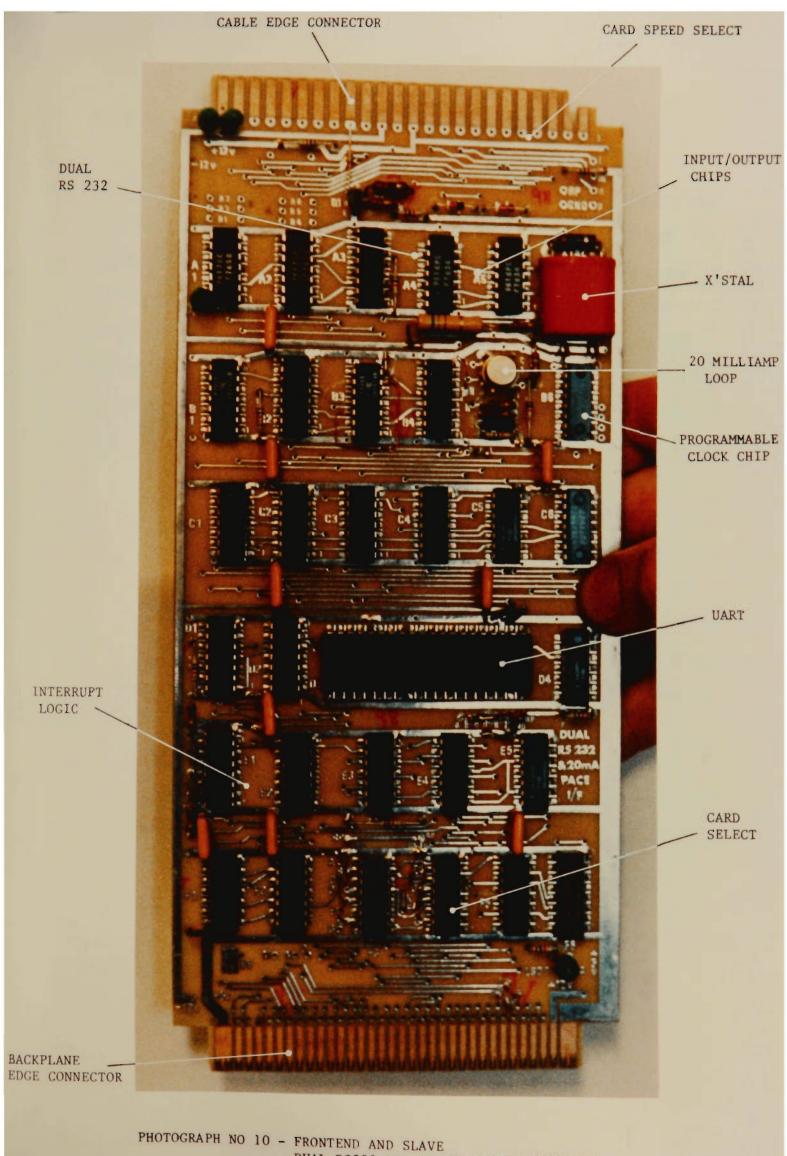

|    | 10 | FRONT-END AND SLAVE INTERFACE        | 57(b) |

.

#### 1.1 BACKGROUND

#### 1.1.1 General

A prerequisite for the overall development, co-ordination and operation of large complex industrial installations is a centralised control system. One example is the system required by the State Electricity Commission of Victoria for the control and monitoring of the mining of brown coal in the Latrobe Valley. As the size of the power stations increase, so does the demand for fossil fuel and, to meet this demand, the open cut operations become more and more complex. To keep the bunkers of the power stations full, a network of dredgers and conveyors in an open cut is used to excavate and transport the coal.

In the early stages of development of the Latrobe Valley coalfields, the supply of coal was fairly easy to co-ordinate because the demand for fuel was low but, as the demand increased and the transport distances involved also increased, it became necessary to optimise the control and monitoring. In practice, a permanent centralised control centre is used and is located remote from the working faces of the open cut. One of the functions of the control centre is to co-ordinate the activities on a daily and long-term basis. Without the control centre, the conveyor network would be most inefficient in its operation. The amount of time lost starting and stopping the conveyors without overall co-ordination would be considerable. A further function of the control centre is to optimise the operations of the conveyor network. Since the early 1960s, large industrial installations have combined both central minicomputer and telemetry techniques to control the activities of a complex process. In the case of an open cut conveyor transport network, the use of computers had been confined to the central control system with hardwired links (a single wire link for each signal monitored) to the plant.

1.1.2 The Process Under Investigation

Typically, an open cut conveyor transport network consists of manned dredgers and stackers and unmanned conveyors, power distribution centres and pumping stations. During start-up, normal operations and stopping the network must be controlled to avoid overfilling and spillage at the transfer points.

With items of plant being located over a wide area there are many remote control functions to be performed, such as the starting and stopping of multiple motor drives, belt slip detection and motor protection. Traditionally, these functions have been controlled mainly by relay based remote control sub-systems with some of the later conveyor control systems of the 1970's using discrete solid state logic.

Each of the traditional style control sub-systems also has an interface between the control sub-system and the telemetry sub-system which, because of the physical connections required, is expensive. The combination of the control and the telemetry sub-systems provides the remote control function from the control centre. For each output from the control centre there was a separate input for the conveyor control sub-system which was connected to the output of the control centre telemetry sub-system. The combined sub-systems form the "remote slaves"

in a large, widely distributed conveyor control network. The search for a simpler interface was one of the major objectives of this study.

In addition to the overall control functions, there are monitoring or data acquisition functions which have to be carried out using the same interface between the control and telemetry sub-systems. The data is used to determine the reason for plant stoppages and hence loss of production. In the case of the unattended plant (conveyor and pumping stations) the importance of the information to be transmitted to the control centre is much greater than with the manned plant. On the manned plant, the information can be supplemented by voice communications.

#### 1.1.3 Developments in Open Cut Control

Between 1966 and 1970, a remote control and monitoring system was installed in the State Electricity Commission's Morwell Open Cut to improve the reporting of plant stoppages. It consisted of a single central mini-computer with 16k of memory and several crossbar scanners for scanning the field inputs. There was no preprocessing of information at the plant, except for starting and stopping sequences and overall control was maintained from the control centre via the central minicomputer.

During the early 1970s, it was realised that the concepts used in the Morwell system would have to be improved for the next system required for the redeveloped Yallourn Open Cut. The Morwell system took six seconds to scan all of the field inputs and it was therefore not always possible to determine the correct chronological sequence of events during the stoppage of a conveyor line because the field inputs could change several times during the scan period.

During the period from 1972 to 1974, the author was involved in investigations into ways of improving the recording of the chronological sequence of events at individual conveyors.

It was not until 1975, when the first microcomputer was installed in the Morwell Open Cut for controlling a pumping station, that an economic solution became available. It was decided to try a prototype microcomputer-based control system. If any major problems did develop, it was possible to man the pumping station on a limited basis without any risk to the coal supplies. Whereas, with a conveyor, if the prototype control system had failed, it would have been more difficult to man the conveyor because of the dusty environment; and further more any stoppages would have affected coal supplies. The Morwell pumping station prototype controller provided the basis for a much larger distributed system and enabled a study to be made of the effects of the industrial environment without affecting coal supplies.

The author was involved in further developments in 1976 when a second microcomputer-based pumping station was installed at the Yallourn Open Cut. The Yallourn pumping station unit included the facility for transmitting eight status signals to an open cut control centre display controlled by the pumping station microcomputer.

These two pumping stations formed the basis for the research into the large scale application of the microcomputer in control systems for open cut conveyor control. Before proceeding with an actual conveyor system, it was decided to investigate the suitability of a microcomputer-based distributed control system. Approval was obtained for the author to investigate the application of microcomputers in a distributed system

with independent control at the remote locations in an overall hierarchical master/slave configuration. This investigation was necessary before proceeding with a major change in philosophy that could affect the operation of the conveyors and hence the supply of coal to the power stations.

0

#### 1.2 OBJECTIVES OF THE RESEARCH

The concepts forming the basis of the research were formulated while working with the Morwell Open Cut control system and the two microcomputer-based pumping stations.

The Morwell Open Cut control system configuration could not always provide chronological recording of events. When an event occurred at a conveyor, the result had to be detected by the central minicomputer immediately. Therefore, an objective of the research was to demonstrate, using a microcomputer-based conveyor control system, that it is possible to record the events at the remote conveyors in the correct sequence regardless of the task being performed by the central system.

The pumping station at Yallourn demonstrated that if several events were to be scanned then an error-free method of transmitting data would have to be adopted.

In addition to the study of the technique of transmitting data, the research also aimed to investigate the problem of the compatibility of transmitted data from different systems. In developing the conveyor transport network, different manufacturer's control equipment had been used on the individual conveyors and this continues to be the case.

A model with a minicomputer master and a distributed microcomputer-based system representing two conveyors linked through high speed serial data links to the control centre was used to achieve the objectives of the study. These objectives can be summarised as follows:

> To demonstrate that independent control and monitoring can be maintained by the remote microcomputer-based sub-systems in the event of the link to the central computer being lost;

To investigate the possibility of improving the chronological recording of data and to provide secure data transmission from the remote sub-systems;

To distribute the central system tasks, making it possible to improve the management reports at the control centre;

To remove single points of failure in an overall control system by distributing the tasks;

To determine the necessary facilities and design techniques required for a microcomputer-based system;

To obtain an understanding of the problems and software requirements associated with using microcomputer-based distributed sub-systems;

To investigate the possibility of removing the expensive interface required between the remote plant control sub-system and the data acquisition sub-system (refer to Section 1.1.2) by

integrating the task of data acquisition in the sub-system control tasks;

To determine the requirements for linking different manufacturers' microcomputer-based sub-systems together;

To study the different types of system configurations possible;

To replace the traditional hardwired conveyor control systems (relay or solid state) and telemetry systems with a more flexible system utilising serial data transmission, better suited to the one-off nature associated with large conveyors;

To demonstrate that it is possible to change a conveyor's control functions by down-line loading (transmitting) new control parameters in the conveyor sub-system.

#### CHAPTER 2 : LITERATURE REVIEW

#### 2.1 TRADITIONAL TECHNIQUES OF OPEN CUT CONTROL

Initially during the 1920's horse-drawn carts were used to transport coal to the power stations then as the coal demand increased the carts were replaced by electric trains. The trains were controlled from a central communications centre with some control of the railway signals. During the 1950s, it was decided that it would be more economic to use conveyors to transport the coal to the power stations. As the conveyor equipment increased in size and number, it became necessary to centralise the control and monitoring of the conveyor transport network. The first major remote control and monitoring system for open cut control used by the SECV was the system installed in the Morwell Open Cut.

The evaluation of technical and economical aspects by the Control System Suppliers showed the expediency of employing both minicomputer and telemetry techniques (using cross-bar scanners), to control the activities of the Morwell Open Cut. From the experiences of Hailstone (5) and the practical experiences of the author, the combination of a minicomputer and a telemetry system, would have been a relatively new technique for the 1960s. It has now been the practice for the past 25 years to use some form of telemetry (frequency division multiplexing, (FDM) or time division multiplexing,(TDM)) or direct wiring to connect the remote plant control systems to a central control centre minicomputer system to provide the overall system for the control and monitoring of the plant.

Other observations made and supported by Jenkins (6) in the area of distributed computers and Prophet (8) in his article ("A new tool for

Production Control") indicated that it would be feasible to implement major control functions by using dedicated computers. The work undertaken independently by Jenkins, Prophet and the author during the early 1970s suggested that a microprocessor-based computer sub-system could be dedicated to performing control and monitoring tasks in a distributed computer system.

The trends in control system techniques during the 1970s is discussed by Sargent and Lundy (9). In their paper they outline the reasons for an increase in the use of solid state control systems leading to the programmable devices of the 1980s.

A problem with the early minicomputer control system used in the Morwell Open Cut was the high cost and complexity of the interconnecting cabling system.

A second problem area highlighted by the Morwell Open Cut system was the low speed of handling data. In order to increase the thoughput of a data acquisition system, the speed of data transmission had to be increased. For the FDM and TDM systems, the environmental conditions determine the speed of transmission and as a result transmission rates of all sub-systems in the system had to be adjusted to the same rate to be compatible with the the slowest link. Deshon (2) indicated that, in the future, it should be possible with the microcomputer sub-system to vary the transmission rate to suit the environment. This is an important aspect for an open cut system which could be subject to electrical interference. The microcomputer would provide the automatic re-transmission of the message at a different speed or bit rate.

In the commercial data gathering systems of the late 1970's, a defined protocol or message format was used to ensure the secure transmission of information, but this was not the case in the industrial systems.

There is a number of transmission and error detection codes available (refer to Appendix F for more details). Transmission codes "Bose Chadahuri", "Baudot", "ASCII" and "BCD" (30) and error codes "CRC-12", "CRC-16" and "CRC-CCITT" (30) are the most commonly used. The message protocol of a data transmission system is basically a set of rules for operating the communication system. McNamara (30) in his book ("Technical Aspects of Data Communications") indicates some of the reasons for these rules, i.e.:

The determination of which part of the message constitutes the control characters or the data portion;

To eliminate duplicate messages, to avoid the loss of messages, and to properly identify messages that are re-transmitted by the error control system;

The determination of which station is going to transmit or receive;

Solving the problem of which message to transmit when there is no data to send;

Solving the problem of which steps should be carried out if message flow suddenly ceases;

The process of initiating transmission in an idle or quiescent system is often complex.

It is unfortunate that computer and peripheral equipment suppliers have developed their own protocols. Nevertheless, certain protocols (refer to Appendix F (p.183)) are now becoming standards by design or through wider use in industry. Standards institutes, such as American National Standards Institute (NASI) and the International Standards Organisation (ISO), are about to adopt certain protocols as standard protocols (12). The Australian Standards Association has published a data transmission standard (25) in an attempt to standardise on data transmission methods. Because of the large number of control equipment suppliers involved in conveyor control systems, data protocol was an important area investigated during this research.

#### 2.2 MICROCOMPUTER HISTORY

In 1971 the Intel Corporation (INTEL) (a large semi-conductor supplier) produced a programmable device as a solution to a request for a flexible control system. The result was the INTEL 4004, the world's first microprocessor (a four (4) bit device). It was very slow by modern computer standards and it could address only 4k bytes of memory, but it was programmable and relatively inexpensive. It was then followed by the 8008, an eight bit device. As stated by Tobias (11) in his paper, microprocessor designs have continued to advance with more powerful and faster devices being developed such as the 16 bit and the bit slice devices.

The microprocessor is very much a hardware oriented product and owes its development to two major factors associated with Large Scale Integration (LSI). One is the technological development of the semi-conductor industry in the LSI area. The other factor is the economics of LSI. Previously, a hardwired control system required a one-off design for each application. An alternative in the 1980s is the microcomputer which can be customised by a change of program. The microcomputer of the early 1980's consisted of one microprocessor chip with a dedicated or defined software program and the required input/output interfaces.

One problem is that most of the advances have been in hardware. There is still an almost universal under-estimation of software problems in industrial microcomputer systems similar to those experienced with the large computers and minicomputers ten years earlier.

#### 2.3 MONITORING AND CONTROL DEVELOPMENTS

With the advent of solid state logic (discrete components, subsequently LSI) the control functions were achieved in a similar manner to the relay systems by using interconnected logical "AND" and "OR" discrete logic blocks (9).

The changeover to solid state control devices was considered a sufficient change in direction for control system design during the 1970s and this made the acceptance of the microcomputer more difficult.

The question was, "Should a company disregard many years of experience and use this new microcomputer technology, considering the problems encountered with minicomputers during the 1960s?". Obviously the microcomputer had to have definite advantages over the techniques in use at the time and, in addition, an understanding of the problems of implementing control requirements using microcomputers was essential if a company was to change its direction.

Falling microcomputer hardware costs and rising costs of one-off hardwired logic systems made it economically attractive to replace traditional methods of remote control and monitoring in large installations. It was feasible to combine remote control, real-time data acquisition and distributed computing at the remote plant locations using microcomputer-based sub-systems linked to a central master. Amendt (1) suggested that a design engineer must consider new approaches to control design and that learning the techniques associated with microcomputer-based systems would prove to be invaluable. At the time of this research, the microcomputer was not widely accepted as a possible method for industrial control and hence there was a need for a study of microcomputer techniques.

South (10) also suggested that the form of remote control sub-systems used at the time could be replaced by a microcomputer-based remote sub-system. There was no preprocessing of information by the earlier control sub-systems but it is now possible to distribute some of the central system's processing of the data to the microcomputer, thereby increasing the effectiveness of the overall control system. This was also supported by Deshon (2) and Dominquez and Tennant (3). The basic aim of the research program was to investigate a method of improving the data throughput of a centralised conveyor control system. This was to be achieved by using microcomputers to control the transmission of the data from a simulated conveyor network without complicating the operating procedures of the system. The following Chapters outline how the microcomputer was adapted to enable the increase in the data throughput for an actual conveyor control system.

#### CHAPTER 3 : THE RESEARCH PROGRAM

#### 3.1 DETERMINATION OF THE SUITABILITY OF MICROCOMPUTER SUB-SYSTEMS

3.1.1 General

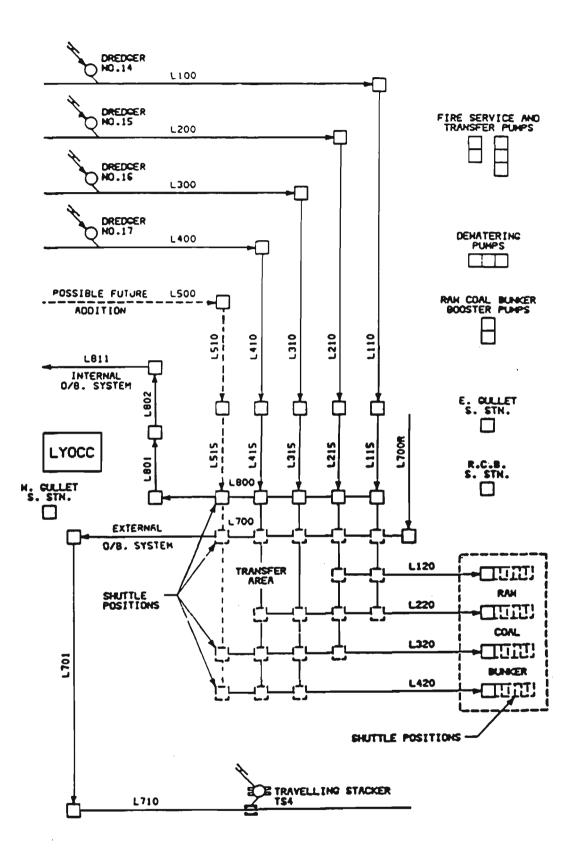

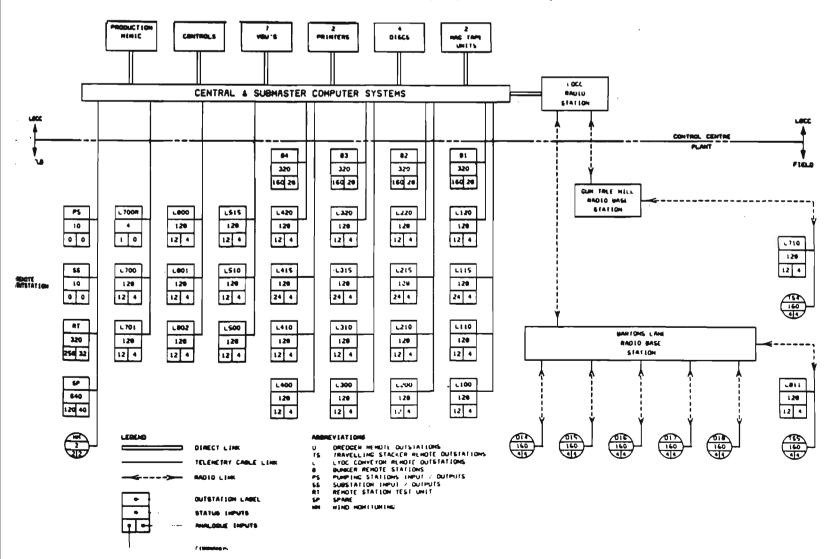

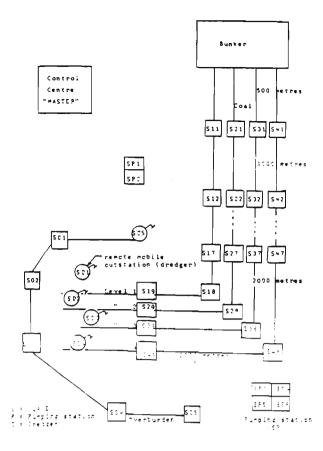

In a large open cut industrial installation, the control system must handle multiple control tasks distributed over a wide area. The layout of the conveyor network as shown by Figure 3.1 represents at least 30 separate plant items. Each conveyor (L100, etc) and dredger (D14, etc) requires a dedicated control sub-system to carry out the control and monitoring functions at each remote location.

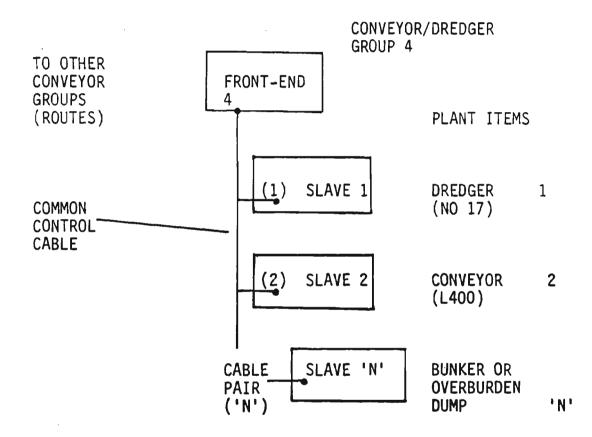

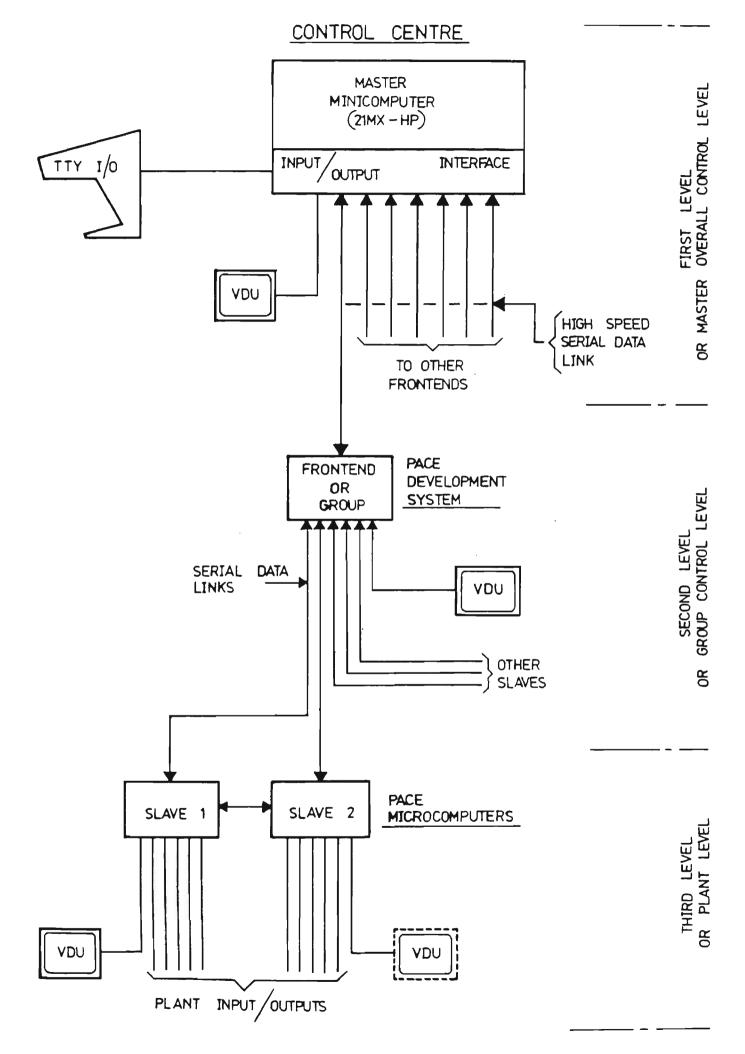

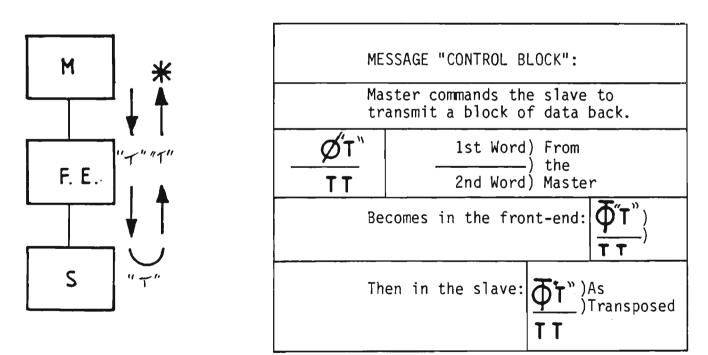

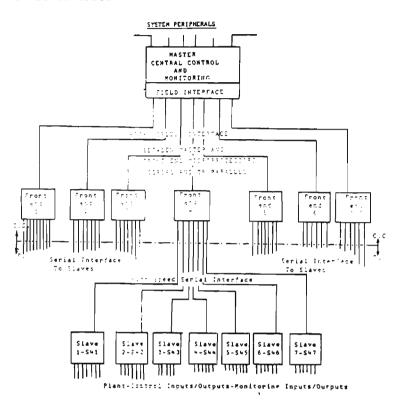

It was demonstrated during the research, using modelling techniques for a limited system, that it is feasible to use a microcomputer-based sub-system for a remote control and monitoring system configured as shown by Figure 3.2. The sub-system tasks were handled by dedicated slave microcomputers, one for each plant item. To distribute some of the central system tasks, the slave sub-systems were controlled by a "Sub-master" or "Front-end" which was in turn controlled by the master.

The natural division between the plant systems, as shown in the open cut layout of Figure 3.1, is the deciding factor in determining the number of slaves controlled by a front-end or sub-master. It is considered undesirable to have plant items on opposite sides of an interchange (or transfer) area or in different conveyor routes connected to the same front-end. To avoid any interaction, or the loss of more than one route (there are 24 possible routes in Figure 3.1), each front-end would have only one dredger group, bunker group or stacker group of plant items directly linked.

FIGURE 3.1 : LOY YANG OPEN CUT PLANT LAYOUT

A model consisting of one master, one front-end (sub-master) and two slave sub-systems was selected for the research program to check the concepts referred to in Section 1.2.

The model was configured in a similar manner to the full scale system of Figure 3.2. Each sub-system was connected by a high speed serial data link to the next level in the hierarchy. The master communicated with the front-end which in turn communicated with the slave sub-system using a defined message protocol.

The model represented the front-end (No 4) for the plant group associated with Dredger No 17 and the two slave sub-systems represented Conveyors L400 (Slave 1-S41) and L410 (Slave 2-S42) (see Figures 3.1 and 3.2). The research program was designed to provide a better understanding of the hardware and software requirements and the associated problems. Because a full scale system for the open cut represented many different facets (i.e. the interconnecting cables, the conveyor sub-systems and the overall control centre system) it was essential that the working model developed include all of these facets. The various levels in the hierarchy are discussed in detail in the following Sections.

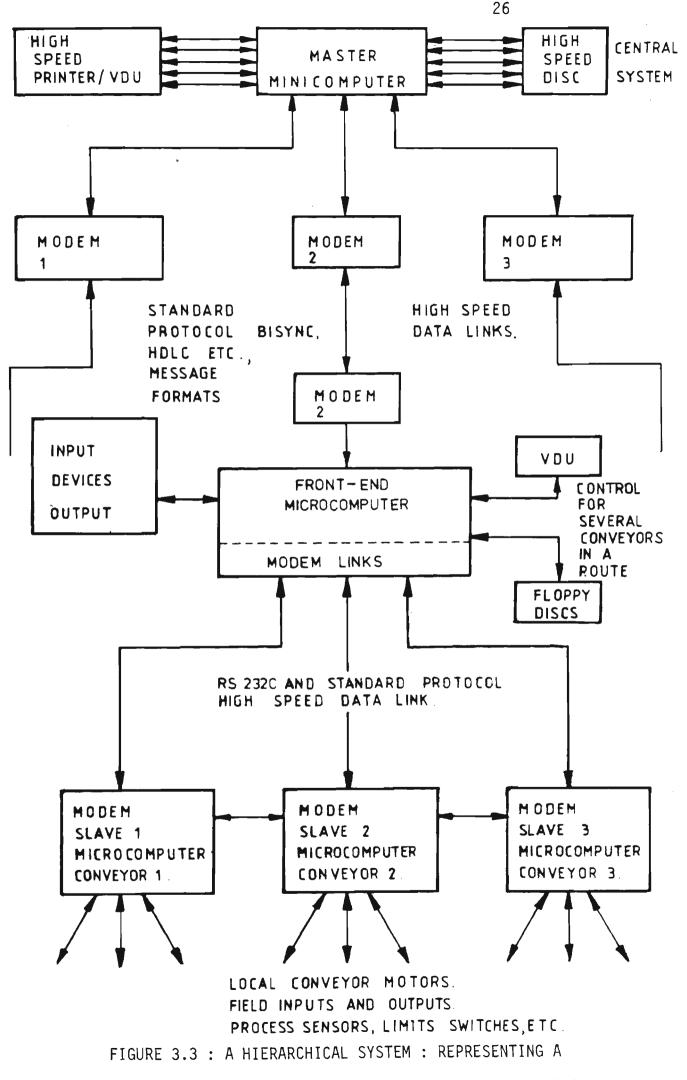

SYSTEM PERIPHERALS MASTER CENTRAL CONTROL AND MONITORING FIELD INTERFACE HIGH SPEED INTERFACE BETWEEN MASTER AND FRONT-END MICROPROCESSORS (SERIAL AND/OR PARALLEL) FRONT FRONT FRONT FRONT FRONT FRONT FRONT -END -END -END -END - END -END -END СС 'N' 1 2 3 4 5 6 СС ┝┽┽┥┿╎╍┥┥ ┝╋╋ ┠╂╌╁╂╁┾┝ ╏╻╻╻╻ ţ F F SERIAL INTERFACE SERIAL INTERFACE TO SLAVES TO SLAVES HIGH SPEED SERIAL INTERFACE SLAVE SLAVE SLAVE SLAVE SLAVE SLAVE SLAVE 1-541 2-542 3-543 4-544 5-545 **6-**\$46 7-547 PLANT-CONTROL INPUTS/OUTPUTS MONITORING INPUTS/OUTPUTS

FIGURE 3.2 : SYSTEM CONFIGURATION

3.1.2 A Single/Multiple Microprocessor-based Sub-system

The sub-systems required to implement the system control strategy would be based on either a single microprocessor or a multiple microprocessor configuration.

3.1.2.1 A Single Microprocessor-based Microcomputer Sub-system

A single microprocessor chip microcomputer had to sequentially carry out the tasks previously performed by the traditional techniques and in addition demonstrate definite improvements.

The aim of replacing proven control and monitoring techniques by a single microprocessor-based sub-system, by the proper scheduling of multiple tasks, was to cover:

. the functions provided by a separate telemetry system;

. data acquisition via high-speed serial data links;

. preprocessing of data at remote plant locations;

. the problems of interconnecting different manufacturers' products using standard interfacing methods;

the standardisation of sub-system hardware by having the differences in the local control algorithms in the individual software programs; a reduction in the central system functions, such as data storage and time 'tagging' (chronological recording) of events.

The microprocessor also enabled the development of an interactive diagnostic facility with VDU terminals which were used in conjunction with a limited English text (question and answer response) as described in 4.3.3.1.

3.1.2.2 A Multiple Microprocessor Microcomputer Sub-system

Instead of using a single microprocessor chip, it would have been possible to develop a sub-system that had multiple microprocessor chips controlling the various tasks. For example six microprocessors could have been dedicated to a sub-system with one for each specific task as follows:

. One for motor control, such as starting sequences or variable speed control, etc;

One for protection monitoring (slip detection, faults, etc);

One for data reduction on the information to be transmitted;

One for data transmission, including control and message protocol emulation (standardisation possible by reprogramming for different formats);

One for the different programming formats: such as relay ladder diagram or logic symbol programming for control;

One for functional independence of tasks, such as having the local control functions separate from the data transmission function.

The multiple microprocessor-based sub-system would have simplified some of the complexity of the software required in the multiple task single processor sub-system. It is the author's view that each software task could have been written for the dedicated device, with less cost and complexity than for the single microprocessor software package. This multiple microprocessor-based sub-system model was not developed. At the time of this research a multiple microprocessor microcomputer was not available, refer to Chapter 7 regarding further work and recommendations.

3.1.3 Advantages and Disadvantages of Microcomputer-based Systems

An advantage of the microcomputer in some of the areas formerly dominated by the minicomputer is that it is an economical solution for single tasks. The conventional approach of using a minicomputer would be to use it for several parallel tasks. This is not ideal because a failure of a multiple-task minicomputer would affect the whole system. Using the model, it was demonstrated that by distributing the tasks over several microcomputers overall control was maintained during failures of the central minicomputer with higher reliability and at a lower cost.

Prior to this research it was anticipated that the use of microcomputer-based sub-systems for control would have the following advantages and disadvantages: Standardisation of hardware, with special software to suit the unique control requirements thus enabling the manufacturer to proceed with the hardware manufacture before completing the system design;

Reduction in development and design of the hardware for each unique situation when compared to the one-off relay systems therefore each design only had to cover the different functional requirements by incorporating suitable software sub-routines;

Reduction in central system dependence so that each sub-system can operate independently during failures of the central system;

Reduction in central system tasks, especially in implementing the control requirements so that the remote sub-system need only transmit status changes as they occur;

Distribution of the central system tasks to the microcomputer based sub-systems to provide increased reliability and flexibility;

Reduction in the overall system hardware costs.

#### DISADVANTAGES:

. Changing to the new microcomputer-based sub-systems would require a change in existing fault finding techniques. In the past, fault-finding was achieved by visually checking through the relay

contacts for electrical continuity which is not possible with the microcomputer;

In some cases, the introduction of a different style of technology (computer-based) would require the retraining of existing personnel;

•

.

The cost of software could increase well above the original estimates if the software programmer does not fully understand the process to be controlled. This is a common problem with software based industrial systems.

These advantages and disadvantages were demonstrated and confirmed by the research work and have since the original study, been reinforced by the developments that have taken place at Loy Yang.

#### 3.2 ESTABLISHMENT OF THE HIERARCHY OF THE PROTOTYPE SYSTEM

#### 3.2.1 General

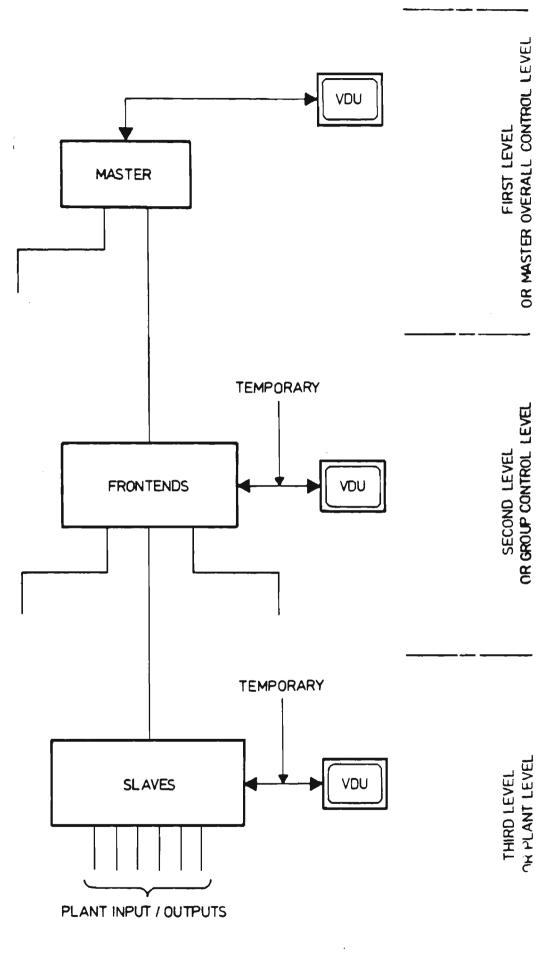

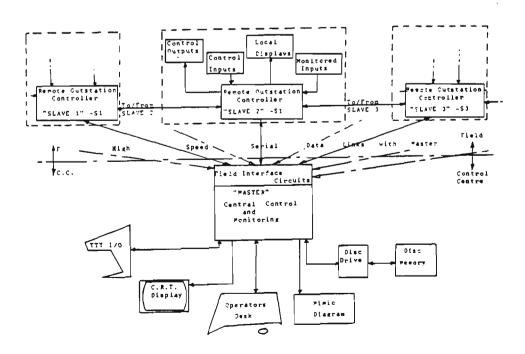

A hierarchical system consists of two or more levels of distributed sub-systems arranged in a pyramid or multi-level formation. At each level, a number of sub-systems (front-ends, slaves) operate in parallel. There is an iterative data transfer between the various levels with a preference for the data transfer down the pyramid to be treated as a command by the lower levels.

For the open cut plant situation considered in this project, the control centre master (a minicomputer) represented the highest level in the hierarchy with the front-ends (microcomputer-based) and the slaves (microcomputer-based) representing the second and third levels respectively. As outlined in Section 3.1.1, a front-end would control the slaves for the conveyors from the dredger to the transfer area or from the transfer area to the bunker as shown in Figure 3.1. The hierarchy of the control system was determined by the basic process to be controlled and the functional independence required between common or parallel tasks, such as a dredger to bunker route, taking into consideration any interchange area.

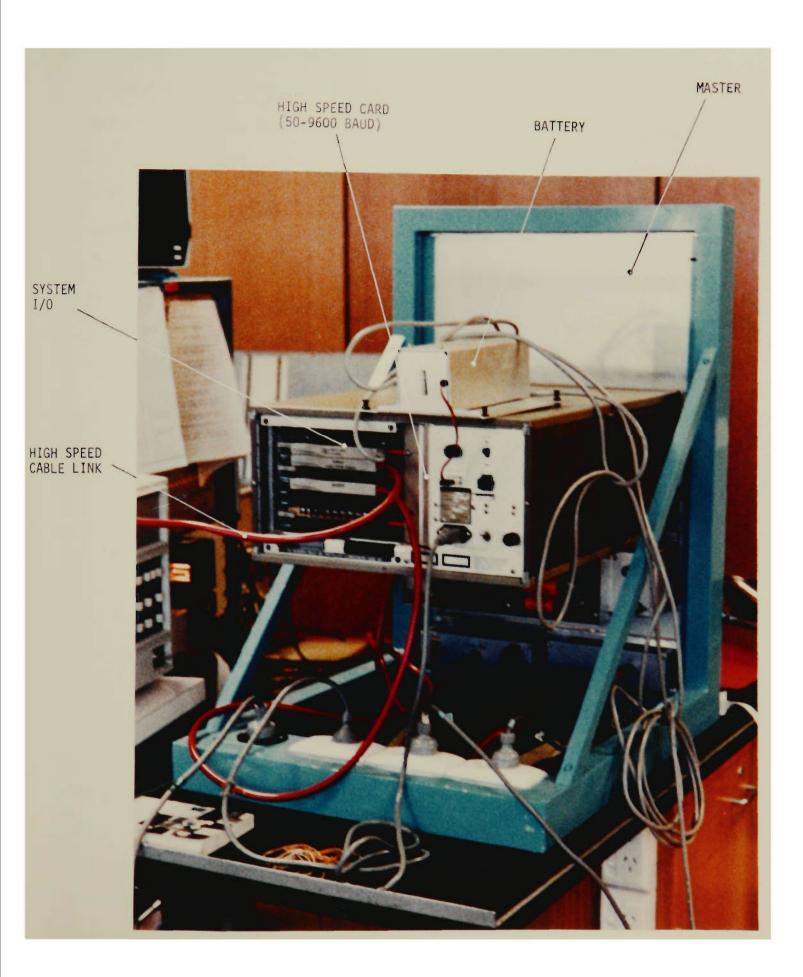

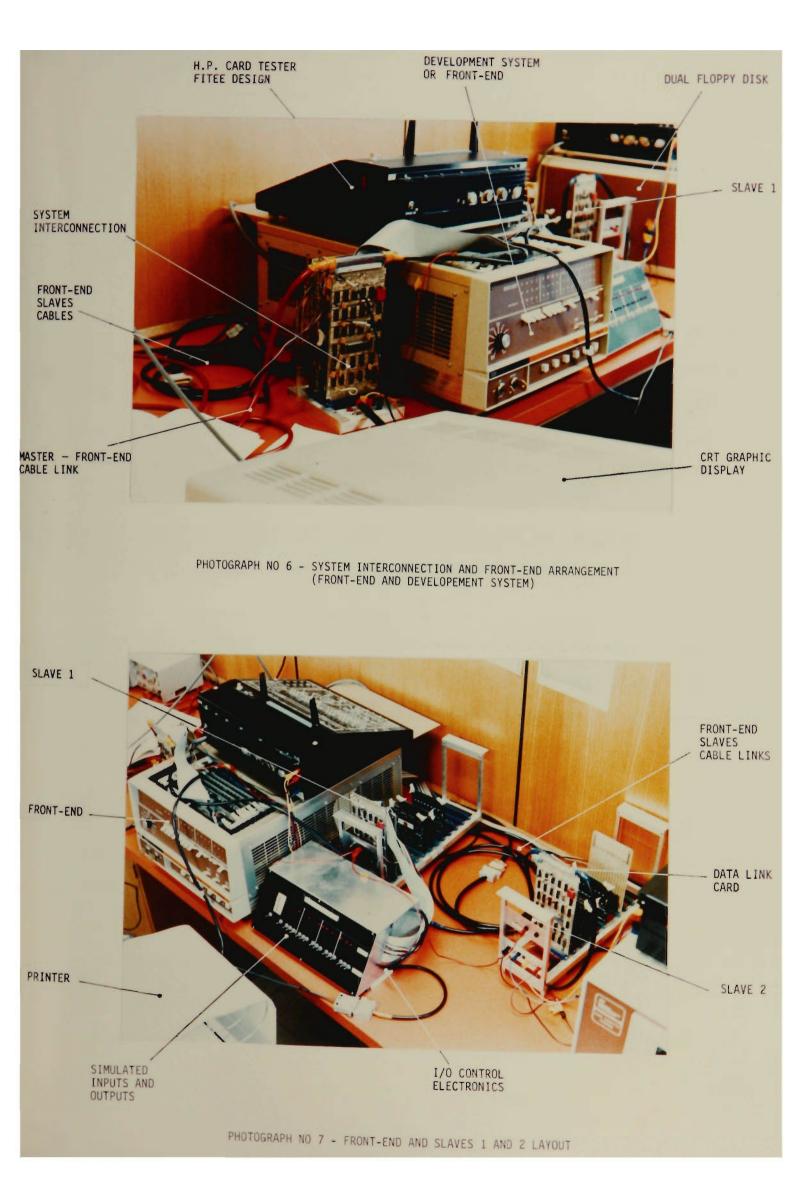

Accordingly, the hierarchy of the prototype system model was as shown in Figure 3.3 and Photograph No 2. This model enabled the requirements of an actual system to be investigated and demonstrated.

PHOTOGRAPH NO 2 - SYSTEM LAYOUT

TYPICAL CONVEYOR NETWORK AS INVESTIGATED DURING THE RESEARCH

The anticipated configuration for an actual situation, as shown in Figure 3.1, (p.16) and Figure 3.3 consists of multiple microcomputers, each one with well defined tasks to perform. For a conveyor network, the overall control is maintained by the master (consisting of single or dual minicomputers). The next level in the system hierarchy is the front-end or sub-master level. Because of the number of front-ends, there must be a defined hierarchy or priority between the front-ends as determined by the conveyor route requirements.

From experience with earlier open cuts the most important group is the top conveyor line in the open cut followed by the lower groups. It is necessary to remove the top layers of overburden and coal in order to keep the alternative routes available. Therefore, the overburden group front-end is the highest priority front-end of the second level.

Similarly, the individual slaves also have a priority rating as determined by the position of the conveyor in the conveyor line. To avoid spillage, the last slave in the line is given the highest priority and to minimise the situation where a slave in the hierarchy was never serviced, a regular check must be initiated by the master.

The model as described in Chapters 3 and 4 is based on this configuration.

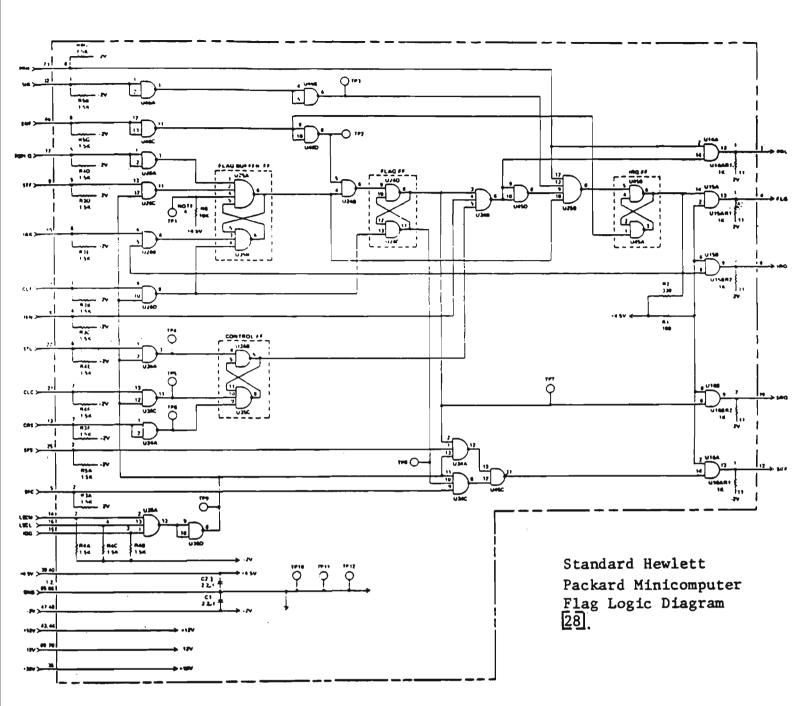

# 3.2.2 Master Sub-system (Photographs Nos 4 and 5)

The 21MX Hewlett Packard minicomputer performed the task of system master for the model. It was controlled through the VDU keyboard which in turn controlled the graphic display of Figure 3.1 and the message transmission to the lower sub-systems (the front-end and the slaves).

Messages to the front-end and slaves (conveyors) were simulated in the master and transmitted via the high-speed serial data link developed for the 21MX minicomputer (refer to Photograph No 5). The message performed the same function as operating a start or stop button at the master. When the message was received by the front-end, it was decoded (as explained in Section 4.3.3.3 on (p.94)) and checked for errors before performing the task or command contained in the message. If the message contained a request for data from the front-end sub-system, the appropriate action of encoding the data was carried out. If the message was for a slave it was re-transmitted to the slaves by the front-end. The central master continued on with other tasks until it received an interrupt from the front-end.

In addition to checking for errors in messages from the master, the front-end also checked messages from the slaves before re-transmitting to the master. This reduced the load on the master because the front-end indicated to the slave that the data received had an error without interrupting the master. This error checking would be important in an actual conveyor network because the interconnecting control cables are located in the vicinity of high voltage equipment in the field and are therefore susceptible to electrical noise.

PHOTOGRAPH NO 4 - MASTER COMPUTER -HEWLETT PACKARD 21 MX - FRONT VIEW

PHOTOGRAPH NO 5 - MASTER COMPUTER -HEWLETT PACKARD 21 MX - REAR VIEW

#### 3.2.3 Sub-master (Front-end) Sub-system

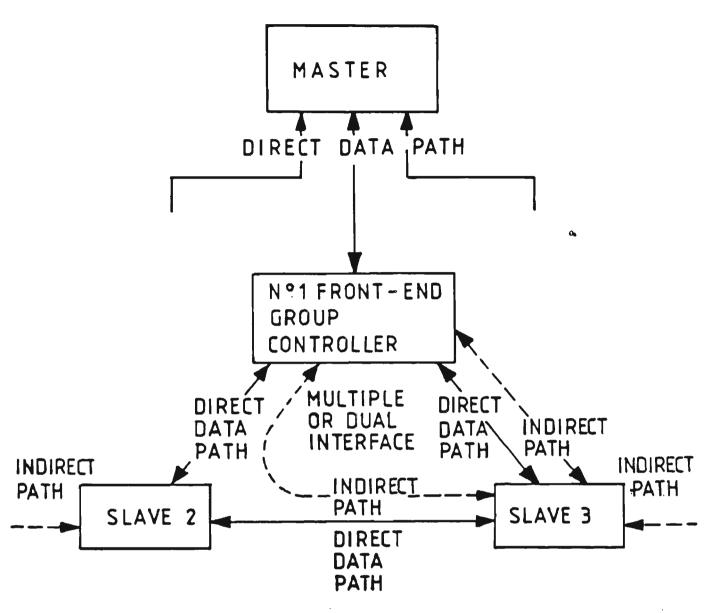

The second level of control in the hierarchy (Figure 3.3) was the front-end computer which was based on the National Semiconductor PACE microcomputer (refer Photograph No 6). The introduction of a front-end in the system strategy enabled the distribution of some of the functions normally performed by the master. In addition, the front-end sub-system also provided two secondary functions:

- The storage of programs for the model (the slave, front-end and master programs were stored on disc and subsequently down-line loaded on request);

- Development facilities were provided for the microcomputer software and hardware via the National Semiconductor prototyping extender card.

The front-end serviced the messages from the master and re-transmitted to the slaves as outlined in Section 4.3.4. In the internal front-end hierarchy, the link to the master had the highest priority after all internal functions of the front-end were serviced.

The internal functions of the front-end were interrupts from the internal clock and the other software sub-routines (e.g. stack handling) during multiple sub-routine servicing. The stack function of the PACE Microprocessor was an internal logic function of the microprocessor chip that handled up to ten transfers of data words or sub-routine return addresses before requiring external memory for storage.

Distributed systems such as the model are subject to many coincident interrupt requests. In the model, in addition to random requests from the connected sub-systems, the front-end was required to service the front-end VDU (refer to Photograph No 2) and acknowledge requests such as time of day in hours, minutes and seconds.

The modular approach of the system model also allowed the removal of the front-end from the hierarchy. The software of the slave was designed to receive the protocol directly from any sub-system. Hence, for a small full scale system (e.g. during the initial development of an open cut with only one dredger and one conveyor line), it would be possible for the slave to be directly connected to the master.

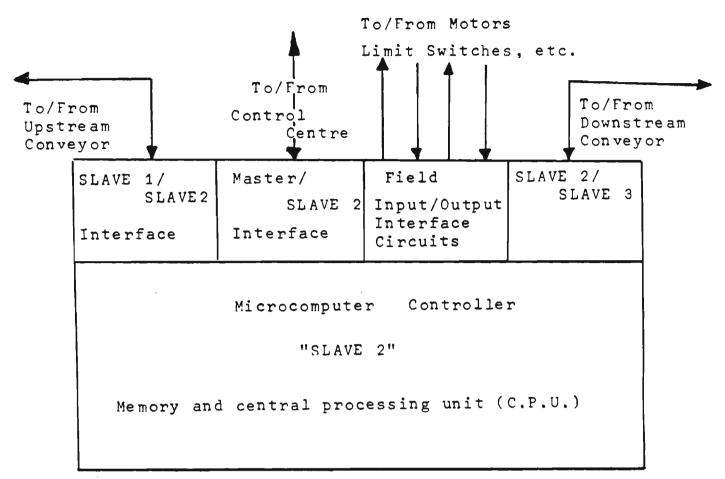

3.2.4 Slave Sub-systems (Photograph No 7)

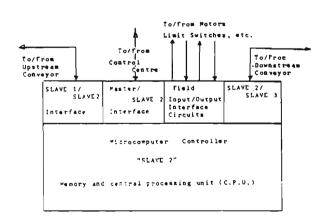

The third level in the hierarchy consisted of the microcomputer-based slave sub-systems and was also based on the PACE microcomputer. Each of the slaves had the same basic data transfer and internal management software packages as the front-end.

The individual slave sub-system which would normally be located at the remote plant sites (conveyors and dredgers) was configured as shown in Figure 3.4.

FIGURE 3.4 : INTERFACE REQUIREMENTS FOR A REMOTE SUB-SYSTEM

The slave consisted of a microcomputer-based sub-system with several high speed serial data links for interconnections with the front-end and adjacent slaves. The hierarchy within the sub-system was established with the direct link to the front-end as the highest priority and the alternative paths through the adjacent slave would be rated according to the direction of flow of the material on the conveyor. The priority of the different links was the same order for the slave as was required for the interconnecting links in the front-end (refer to Section 3.2.3). The slave was also rack mounted for ease of change or card replacement. The loss of small elements such as individual slaves in one conveyor route would be more acceptable than the major losses possible with more traditional techniques which could take out more than one conveyor route.

## 3.2.5 Methods of Communication

In the development of the hierarchical system, consideration was given to the way the sub-systems were connected together. At the hardware interface level, the following factors were taken into account:

- There was a variety of speeds used by the devices and sub-systems to be interfaced which was accommodated by the selectable logic on the interface card;

- The devices used were either current or voltage driven;

- The voltage requirements for voltage driven devices used the industry standards EIA (RS-232C) and CCITT (V24);

- The hardware interfaces had to be compatible with other serial devices and with existing software packages.

Once the hardware interfaces for the model had been designed, it was then necessary to decide if the configuration would be a party line or radial communications network.

## 3.2.5.1 Party-Line

In a party-line network, at the slave or front-end level, each sub-system would share a common data cable pair. All units would receive the same message but only the one addressed would respond.

#### 3.2.5.2 Radial

In a radial network, each sub-system would have its own dedicated data cable pair radiating from the central sub-system. Sub-system identification is not necessary since the identification is inherent in the layout. The choice of the method to be used usually depends on the polling frequency, response time and the number of cable pairs required. Generally, in an open cut situation the smallest cable used (based on the consideration of its mechanical strength) would have 10 pairs, hence the one cable could support 10 sub-systems.

Following consideration of the cable pairs available and the speed required to identify the sub-system, a radial communication network was chosen for the prototype system.

## 3.3 INVESTIGATION OF THE DATA TRANSFER TECHNIQUES FOR THE MODEL

#### 3.3.1 Modes of Operation

Most of the traditional modes of operation of communication systems are also applicable in hierarchical microcomputer systems, such as:

- . polling (group, individual) of sub-systems by the master;

- . interrupt driven communication with the sub-systems;

- . continuous communication with the sub-systems;

- priority messages to and from the sub-systems.

Use of the microcomputer enabled a system model to be developed which used basically an interrupt driven and a time initiated polling structure.

There were two methods of operation which were fundamental to the overall system structure; interrogation on interrupt from the sub-systems and time controlled polling of the sub-systems. The polling mode was controlled by the clock (sub-routines were initiated on a time flag) while the interrupt mode was controlled by the hardware and the system hierarchical structure.

## 3.3.1.1 Interrupt Operation

In a steady state system under normal program execution, the sub-systems would be fairly inactive, stopping and starting motors, etc, but continually updating their record of the previous status of the plant. This mode would reduce the flow of data to and from the master computer by comparing the previous status (i.e. the status that was last transmitted to the master, which was stored in memory) to the current status. If a sub-system does not transmit, the master will assume the same condition exists; for example, if a slave has reported that a motor has stopped it will not report its status again unless it is restarted or the master requests a status check.

## 3.3.1.2 Polling (or Continuous) Operation

Polling, by definition follows a predetermined sequence in its acquisition of data. Instead of permitting any sub-system to report status changes as they occur, a polling system permits each sub-system to

report only when it is requested to do so. In this way, data transmission is completely controlled by the master.

Polling systems have no way of giving priority to important information. Each critical alarm must wait until it is next scanned before the master can act on the data. This is also one of the major problems of the traditional systems using relay or solid state logic. These earlier systems have no processing capability, hence there is no way of assigning priorities. A combination of the above modes can reduce the effect of these problems. The model allowed:

- . faster scanning;

- . checking for the presence of altered data;

- . preprocessing of information;

- . increased message efficiency;

- . system response improvements.

3.3.2 The Message Protocol of the Model

Distributed microcomputer sub-systems require a structured message system similar to the earlier telemetry systems outlined in Section 2.1. In data transmission systems, data can be transmitted either synchronously or asynchronously. Synchronous transmission means that the data being transferred is in synchronisation with a timing signal or a strobe pulse. In synchronous systems, the strobe pulse is transmitted with the data. The strobe signal notifies the receiving device that valid data is available. In serial asynchronous systems (such as the one under study), synchronisation is provided by the active data transmitted or received. The transmission of a particular data pattern consists of a start bit, eight data bits and one or two stop bits; testing for a particular data word "SYN" provides the synchronisation of the data blocks while the start and stop bits provide the synchronisation of each character received.

One of the advantages of a serial system is that it lends itself to transmission over telephone cables. The serial digital data (refer to Section 4.2.4) is converted to a frequency signal by a modem, placed onto a voice-grade cable and converted back to serial digital data by the receiving modem at the other end of the line.

In the model a defined protocol or message format was used to ensure the secure transmission of information.

The information outlined in the Literature Review of Chapter 2 and Appendix F regarding industry standards and the requirements of the Australian Standards Association was used as a guide for the protocol of Figure 3.5 (p.41) as adopted for the research model. The system protocol also included the following standard transmission control characters:

"SYN" (Synchronous idle) - a signal from which synchronism may be achieved;

"SOH" (start of heading) - first character of a heading;

"ETX" (end of text) - terminates a text;

"NAK" (negative acknowledge) - message not accepted;

"ENQ" (enquiry) - request for a response;

"EOT" (end of transmission) - indicates the end of the message;

"ACK" (acknowledge) - an affirmative response to the transmitting sub-system;

"STX" (start of text) - used to precede text and terminate a heading;

"FS" (File separator) - used to separate blocks of data.

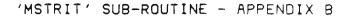

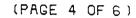

Secure data transfer between the sub-systems was achieved using the protocol of Figure 3.5, as developed by the author, refer also to Appendix B, (p.153) for an example of the software sub-routine that used the developed message protocol to transfer data between the sub-systems.

| വ                        | ω                    | (2)               |                    | (4)                 | (5)                | <br>                       | (2)              | ω                  | (2)                                     | (3)                |

|--------------------------|----------------------|-------------------|--------------------|---------------------|--------------------|----------------------------|------------------|--------------------|-----------------------------------------|--------------------|

| 8 Y W n                  | \$0H5                | HEADER<br>NO.1    | S<br>0<br>H1       | HEADER<br>NO.2      | ERROR<br>Code      | F<br>S <sub>1</sub>        | CONTROL<br>Block | S<br>T<br>X1       | INFORMATION FIELD<br>( IF ANY )         | E<br>T<br>X,       |

| 'n' 8-811<br>('n' 87768) | 6 8-0IT<br>(8 8YTE8) | 8-0IT<br>(1 8yte) | 18-817<br>11 VORD1 | 2 8-817<br>(1 WORD) | 18-817<br>(1 ¥080) | 18-81<br>118-81<br>1 10801 |                  | 18-8[7<br>11 VORD1 | '0' T0 'm' 18-017<br>('0' T0 'm' V0008) | 18-817<br>11 1990) |

| STHOMEONIEING<br>FIELD   | MODELES FIELD        |                   |                    |                     |                    | CONTROL FIELD              |                  | DATA FIELD         |                                         |                    |

#### MESSAGE FORMAT

NOTES:

SYNCHRONISING FIELD :

(1) SYNCHRONISING CHARACTERS (SYN) / MAXIMUM OF TEN ERROR BYTES BEFORE AN ENQUIRY IS SENT TO THE TRANSMITTING SUB-SYSTEM.

ADDRESS FIELD :

- (1) START OF HEADING BLOCK NO.1 (SOH) , SIX CHARACTERS REQUIRED TO ESTABLISH A CORRECT SEQUENCE.

- (2) "HEADER NO.1" ; DATA LINK CHANNEL ADDRESS FOR THE NEXT SUB-SYSTEM LEVEL

- (3) START OF HEADING BLOCK NO.2 (SOH) , A SINGLE CHARACTER IS USED TO SEPARATE THE TWO HEADER BLOCKS.

- (4) "HEADER NO.2" J SECTOR NUMBER (MAXIMUM 256) IS THE MOST SIGNIFICANT BYTE. THE SUB-SYSTEM MEMORY IS SUBDIVIDED INTO 256 SECTORS.

WORD NUMBER (MAXIMUM 256) EACH SECTOR IS DIVIDED INTO 256 WORDS.

- (5) ERROR CODE , A CHECKSUM CALCULATION OF THE INFORMATION FIELD FOR ERROR CHECKING.

CONTROL FIELD :

- (1) FILE SEPARATOR (FS) # USED TO SEPARATE THE CONTROL FIELD FROM THE ADDRESS FIELD.

- (2) THE "CONTROL BLOCK" CONSISTS OF THREE WORDS ;

- · COMMAND WORD NO.1 FOR THE RECEIVING SUB-SYSTEM (16 BIT)

- COMMAND WORD NO.2 FOR THE NEXT LEVEL (THIRD LEVEL) AND THE FOLLOWING (THE FOURTH). ONE BYTE FOR EACH COMMAND.

- . THE RELOCATABLE ADDRESS POINTER FOR THE INFORMATION BLOCK.

DATA FIELD :

- (1) START OF TEXT (STX)

- (2) "INFORMATION FIELD" , ALLOWS FOR A COMPLETE RELOAD OF THE RECEIVING SUB-SYSTEM MEMORY (UP TO 65,536 WORDS). VARIABLE LENGTH DATA.

- (3) END OF TEXT (ETX)

FIGURE 3.5 : PROTOCOL FORMAT ADOPTED FOR THE RESEARCH

S

In addition to the standard control characters used in the system protocol of Figure 3.5, the standard control characters were also used to acknowledge messages or errors in messages.

The incoming message was loaded into a receive buffer and if at any stage during the transmission of data an error was detected, a standard error code, negative acknowledge "NAK" or enquiry "ENQ", was sent to the transmitting sub-system. It was possible to terminate the data transfer at any stage by transmitting an "EOT" - end of transmission character. If the data was received without an error being detected, the acknowledge signal "ACK" was transmitted by the receiving sub-system.

From Figure 3.5, it can be seen that the protocol developed followed the basic rules for information protocols as outlined in Appendix F. The protocol included a synchronising field, an address field, a control field and a data field. In addition, the system used the standard control characters such as "SYN" synchronise, "SOH" start of heading and "ETX" end of text.

Sections 4.3.3.3 (p.94) and 4.3.4 (p.99) explain how the system protocol and, in particular the control characters, were used to clarify two important areas of investigation:

The data transfer techniques required for system modelling;

The operating strategy of the model.

## 3.3.3 Error Detection in the Model

For error detection within the model, it was decided to develop the hardware error signals (refer to Section 4.2.4.4 on (p.73)) and a checksum sub-routine (refer to sub-routine "CHEKSM" as explained in Section 4.3.3.2, (p.89)) in order to investigate the requirements for data transfer and its security.

Each eight bits of the incoming data was subjected to the hardware error checks, followed by a test for particular 8-bit characters (i.e. "SYN", "SOH", "STX" and "EOT") as outlined in the above section. Once the data transfer was complete, it was then subjected to the checksum test. For an actual system, one of the cyclic redundancy checks (CRC) as outlined in Appendix F3 could be used. Using the more complex CRC code, instead of the checksum approach as used, would only have been an additional software coding exercise. This could be included if there was any further development of the model but was not implemented due to the time constraints.

#### CHAPTER 4 : THE EXPERIMENTAL MODEL

## 4.1 DEVELOPMENT OF THE MODEL

The model developed for the research represented the fundamental units required for the investigation of a microcomputer-based conveyor transport control and monitoring system. The configuration selected enabled the study of data transfer techniques within a hierarchical structure and comprised a hypothetical control centre master with several lower order sub-systems. In addition, the feasibility of interconnecting the lower order sub-systems via the alternate data path between the sub-systems was investigated.

In an open cut plant network, the operational and environmental constraints determine the basic parameters (system reliability, linking and construction) of the industrial control system. It was these parameters that were used as part of the criteria for the model. An understanding of the requirements of each one was gained by the author during many years of working with the application of control systems for open cut plant.

An overall plant control and monitoring system should not degrade the security of the coal and overburden removal networks. The configuration selected for the model meets the security requirements since any major failure of a system would be due to damage to the interconnecting cable, see Figure 4.1 (p.45). As can be seen from Figure 4.1 and the conveyor plant layout, Figure 3.1 (p.16) it is not possible to bypass a single plant item (dredger or conveyor) in the middle of a conveyor line. An outage of the conveyor route could be caused by the loss of one of the

individual slave (conveyor) sub-systems or by the loss of the cable along the conveyor structures which form the routes from the dredgers. For example, the L400 to L415 conveyor group (Figure 3.1, (p.16)) has only one cable with up to 24 pairs, damage to the cable or a failure of front-end No 4, as shown in Figures 3.2 and 4.1, would have the same effect.

FIGURE 4.1 : COMMON CABLE FOR SUB-SYSTEMS OF THE SAME GROUP

Therefore, the use of a front-end in an open cut control system model, with a small reduction in the overall hardware reliability, was justified by the increased benefit of improved security of the overall control system. The front-end provided the opportunity for limited control at the control centre during any outage of the master, see Section 5.1.1. Any other configuration would require control at the remote conveyor (slave) locations during failures of the master which would involve long delays while trying to co-ordinate the overall control. For comparison purposes, the hardware and software were also developed to allow for the case where the master controlled the slaves without the front-end. This was achieved by developing the software in the lower sub-system levels to a point where the front-end sub-systems became transparent by re-transmitting any messages received to the next level in the hierarchy (refer to Section 4.3.4) or by direct connections between the master and slaves.

Another configuration, using the same hardware and software in a multiple slave daisy chain arrangement is also possible, but due to the time constraints of the project this configuration was not investigated.

FIGURE 4.2 : SYSTEM CONFIGURATION OF THE EXPERIMENTAL MODEL

The model was therefore developed around the natural constraints of the open cut application and the sub-systems available. The completed model consisted of a single master minicomputer, one group front-end sub-system connected to two slave sub-systems representing two conveyors as shown in Figure 4.2.

4.2 THE HARDWARE REQUIREMENTS OF THE MODEL

## 4.2.1 Master Computer

The minicomputer selected for the master computer in this project was typical of the type of computer that has been used for this task since the early 1960s and as Hewlett Packard support facilities were already available at the Institute, the HP-21MX computer was selected as the master computer.

The master computer (21MX) was configured with a high speed paper tape reader, teletype, Real-time clock and a graphic display VDU. As part of the project, special high speed serial interfaces were designed for connection to the system VDU and to the other sub-systems (front-end and slaves) as shown in Figure 4.2.

With the 21MX computer, it is possible to service up to 56 distinct interrupts, each of which has a unique priority code associated with a corresponding interrupt location in memory and input/output interface channel. This is designed to suit the different peripherals and high speed data interfaces of the master. Within the hierarchy of the modelthe channels were selectively enabled or disabled under program control, thus switching the device connected into or out of the defined interrupt structure. Each device (CRT, VDU, Real-time Clock, tape reader and front-end) was assigned a priority, based on the conveyor plant configuration of Figure 3.1 (p.16) and the expected master system functions. The selection of priorities enabled a systematic sequence for servicing interrupts from the different devices. It was also required that the high-speed devices should not have to wait for the low-speed device transfers.

The plant configuration of Figure 3.1 (p.16) consisting of five dredgers at different coal levels, set up the priorities for the model with the external overburden conveyor line as the highest priority followed by the next level down. For the model, consideration was only given to the priorities between the devices connected. Logically, the Real-time clock had the highest priority followed by the front-end interface, with the VDU unit for display purposes as the lowest priority.

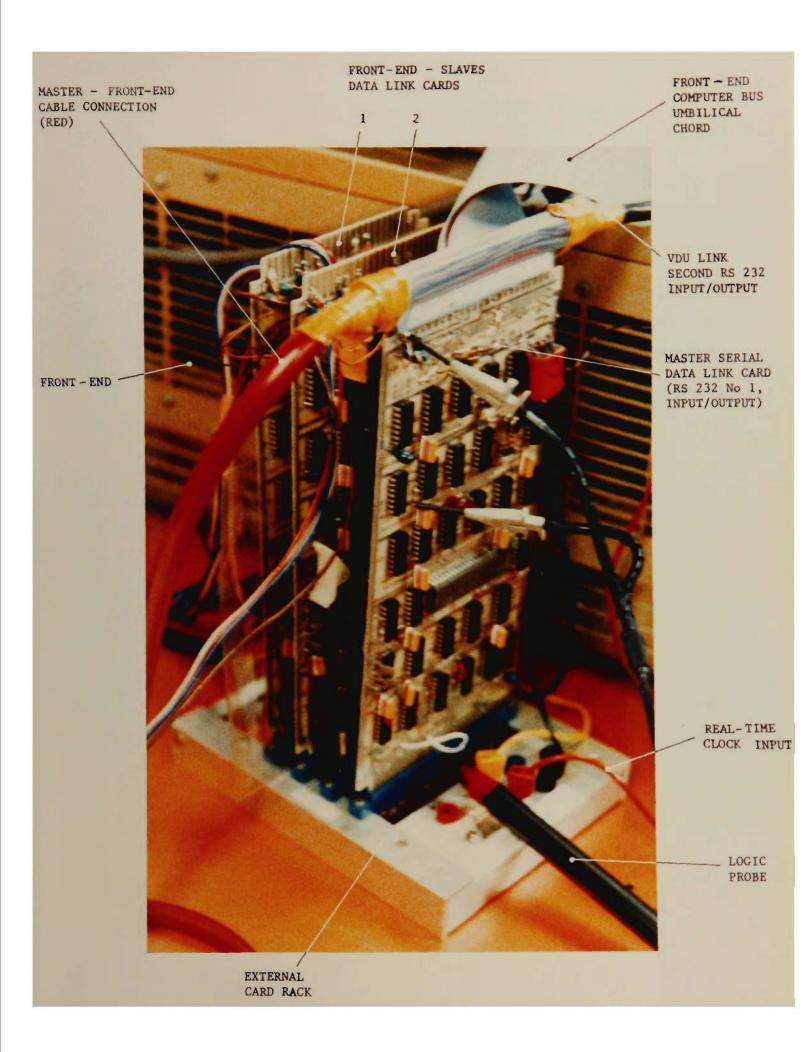

## 4.2.2 Front-end Computer

The front-end (Photograph No 6 (p.32)) of the model was a National Semiconductor Full Scale PACE microcomputer development system. The PACE development system consisted of 12k RAM memory, a high speed paper tape reader, a teletype, VDU, dual floppy discs. Several special high speed serial data links for communication with the slave and the master computers were developed as part of the project. The development system enabled each microcomputer-based sub-system (front-end and slaves) to be developed from the basic cards and components available.

The locally supported PACE microcomputer was chosen as the most suitable device for the task in order to avoid delays and problems with replacement hardware. In addition, the facilities available in the Electrical Engineering Department at the Footscray Institute of Technology provided supplementary support to a PACE microcomputer-based system study. All of the basic principles applied to the PACE microcomputer during the research can be applied to other microprocessors.

In addition to the standard cards, use was made of the prototyping facility of the development system (front-end) in order to develop the special high speed data links of the slaves and front-end and to enable the interconnection of the sub-systems to the front-end as shown by Photograph No 3.

Handling multiple tasks is an important function for computer systems and languages. The sub-systems of the model had to be able to handle several concurrent tasks in their combined local control and data transmission

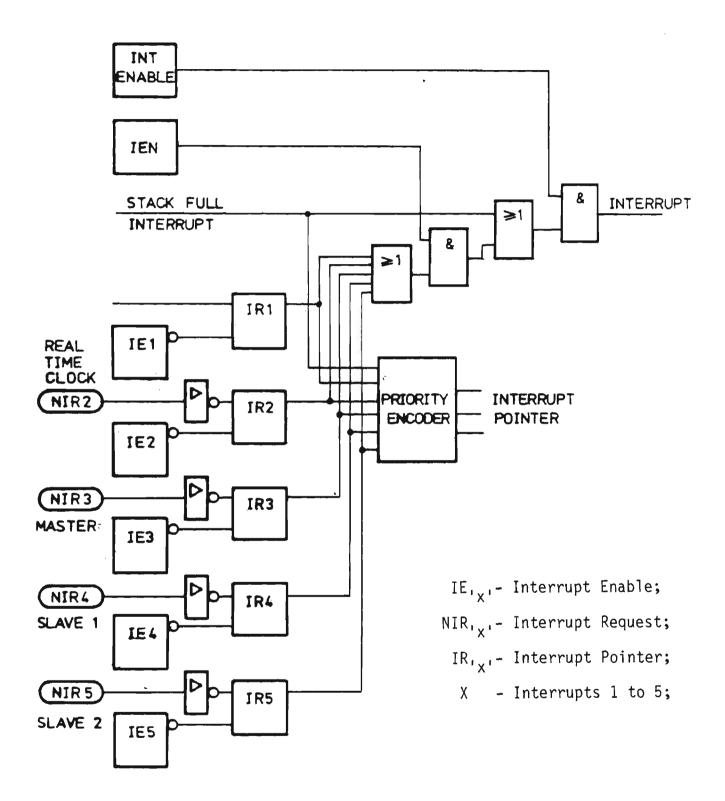

modes. To achieve the hierarchy for the front-end and the slaves, use was made of the 6-level priority interrupt structure of the PACE microprocessor shown in Figure 4.3. (p.53).

Each level was provided with a software driven enable "(IE2-IE5)" plus the overall enable "IEN". When an interrupt request (NIR1-NIR5) occurred, the associated request latch (IR1 to IR5) was set, if "IEN" was true then an interrupt was generated and recognised. The interrupt pointers or addresses of the various interrupt service sub-routines were stored in the memory (refer to Section 4.3.3.3 (p.91), regarding stack handling for more details).

Each of the interrupt levels was assigned a task in the system hierarchy. The highest priority interrupts were assigned housekeeping tasks such as stack or multiple sub-routine handling and Real-time clock servicing. The remaining interrupts were used to form the external hierarchical structure. See Section 4.3.3.3, on interrupt handling for further details. For systems that require expanded user interrupts, the technique outlined in the PACE user's manual (31) could be adopted, but for the model, an expanded interrupt capability was not required.

FIGURE 4.3 : PACE INTERRUPT SYSTEM AS IMPLEMENTED IN

## 4.2.3 Slave Computer

The hardware requirements of the slave computers were not as involved as those of either the master or the front-end. The slaves for the model consisted of the standard general purpose National Microcomputer cards (CPU, ROM and RAM). In addition a Real-time clock card, input/output panel and interface control card and a high speed serial link card was designed for the slave.

. The Central Processing Unit (CPU) card contained the microprocessor, a crystal controlled oscillator and data buffers. The flag and control sections provided the external signals for the connection to the other cards. Data transfers between the CPU and memory or peripheral devices were carried out over the 16 bit parallel input/output data bus.

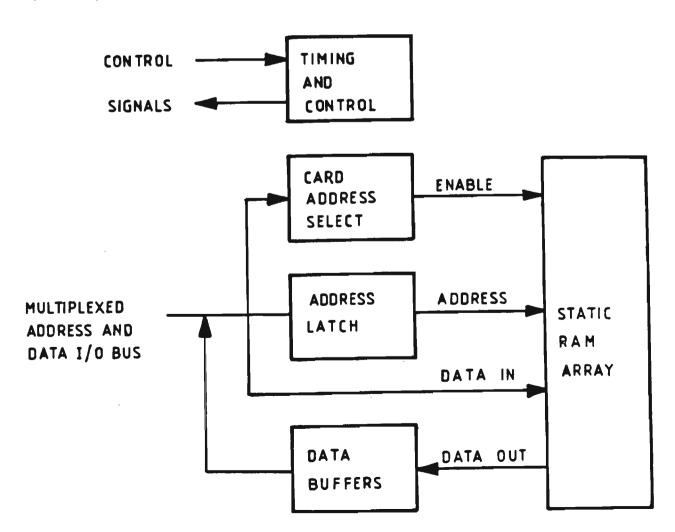

EIGURE 4.4 : RAM BLOCK DIAGRAM

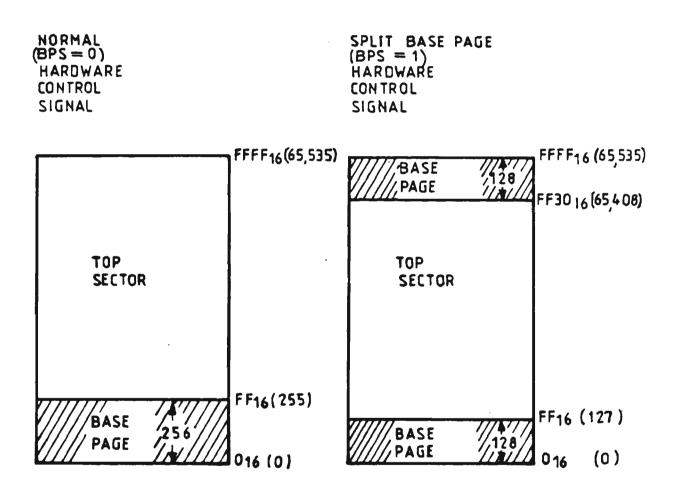

. The National Semiconductor Memory card, as shown by the block diagram of Figure 4.4, consisted of the RAM or ROM memory chips – depending on the type of memory required. The address was latched to select the memory location for data transfer.

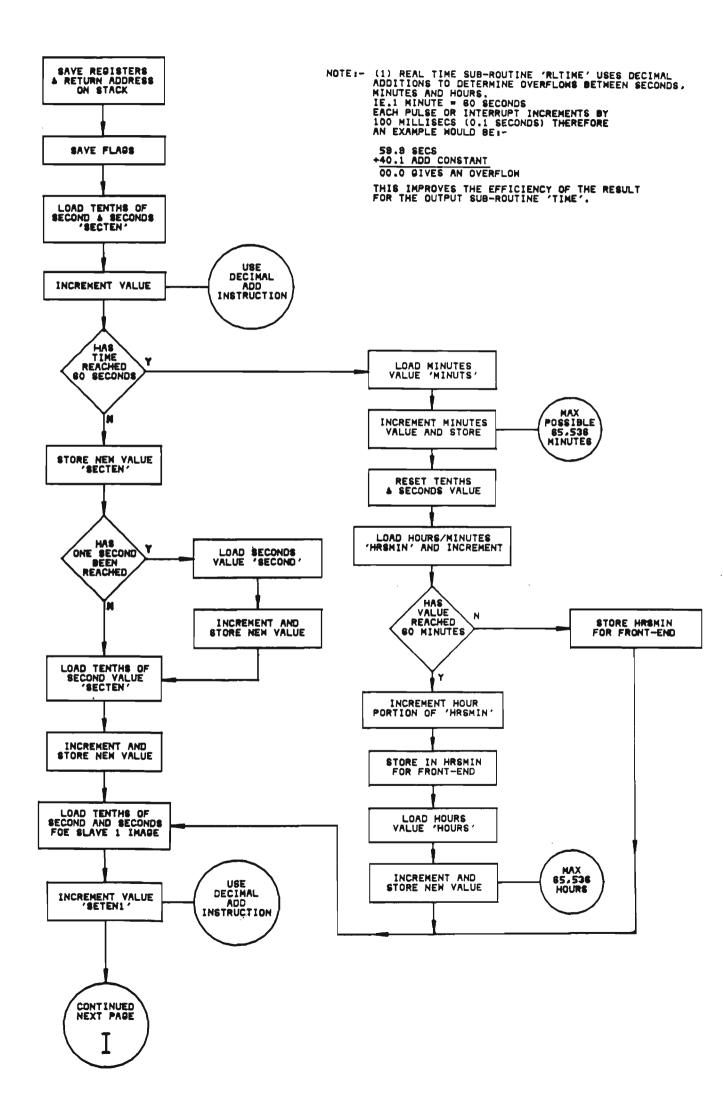

. The Real-time clock card was another important area of the real-time control situation under investigation. The Real-time clock card was specially customised to suit the timing requirements of the software programs and provided a predetermined pulse for the Real-time clock sub-routine. All events at the slave sub-systems were related to the time of occurrence and were therefore referenced to the actual time. In addition, the scheduling of the software sub-routines for execution was controlled by the Real-time clock pulses. The time period was fixed at the smallest value required (100 milliseconds), while larger periods were determined by the software sub-routines.

## 4.2.4 High Speed Data Interfaces

## 4.2.4.1 General

In addition to the standard computer cards and input/output devices used and adapted, there was a need for a high speed interface card, as shown in Photographs Nos 8 and 10, in order to link the sub-systems (master, front-end and slaves) of the model together and for interfacing the teletype and VDU to the computers. At the time of the research, the suppliers of the hardware had not developed a suitable application card which met all of the requirements of Section 3.2.1. The high speed data links were an essential part of the model, hence it was necessary to design and produce several cards for the model.

The hardware was developed using prototyping cards consisting of dual in-line integrated circuit sockets with wire wrap pins or soldered connections, as shown by the prototypes in Photographs Nos 8, 9 and 10. The appropriate cards were tested by using either the PACE development system or the Hewlett Packard card tester.

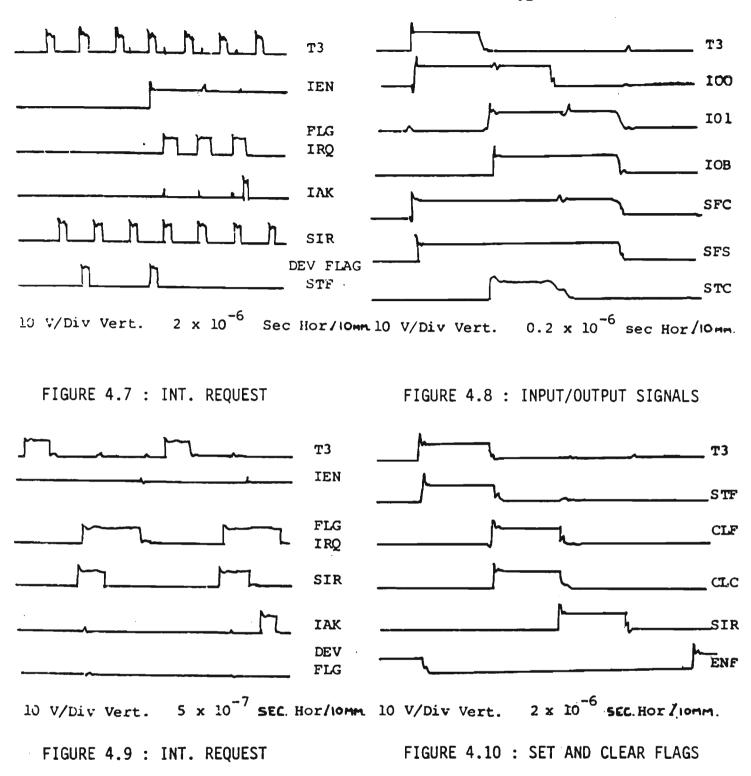

The following Sections (4.2.4.2 and 4.2.4.3) describe in block diagram form how the logic functions on the cards were implemented. As with most computers, the 21MX-HP minicomputer and the PACE microcomputer processor cards did not directly drive the peripheral devices connected, therefore it was necessary to analyse the backplane signals as detailed in the handbooks with the aid of a camera mounted on a high speed cathode ray oscilloscope in order to design the interface cards required.

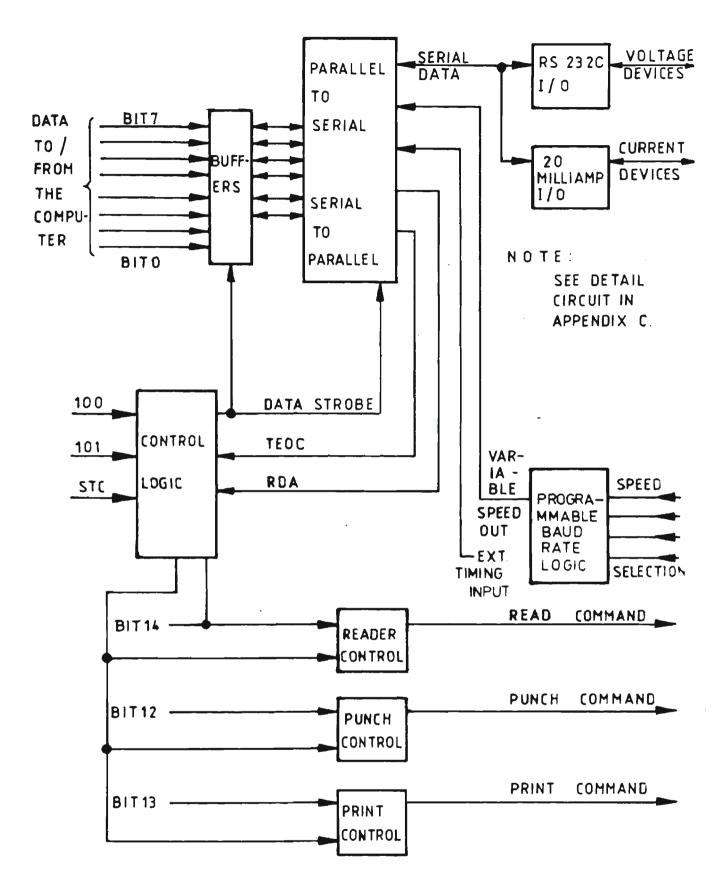

DUAL RS232 AND 20 MILLIAMP INTERFACE - HIGH SPEED SERIAL DATA LINK 4.2.4.2 The Basic Building Blocks of the High Speed Interfaces

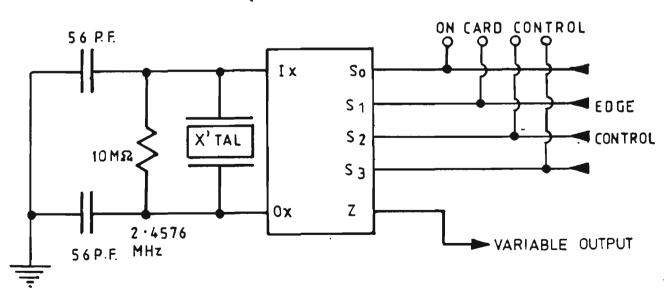

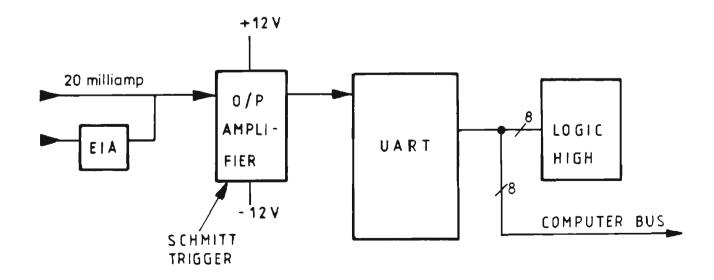

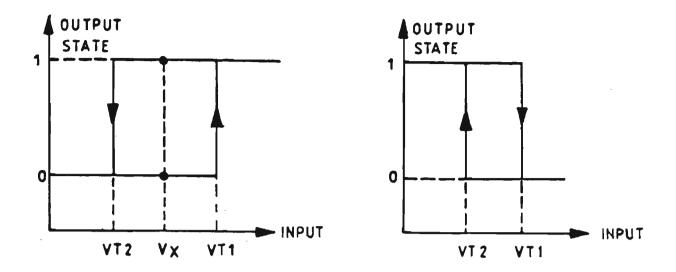

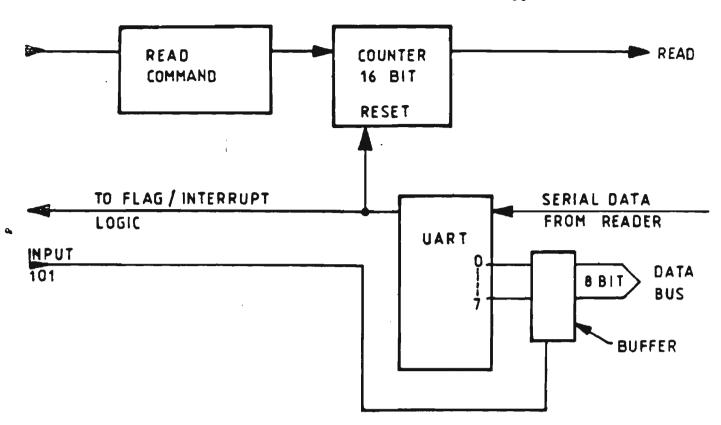

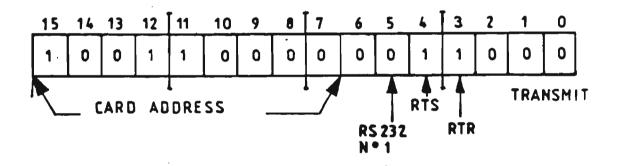

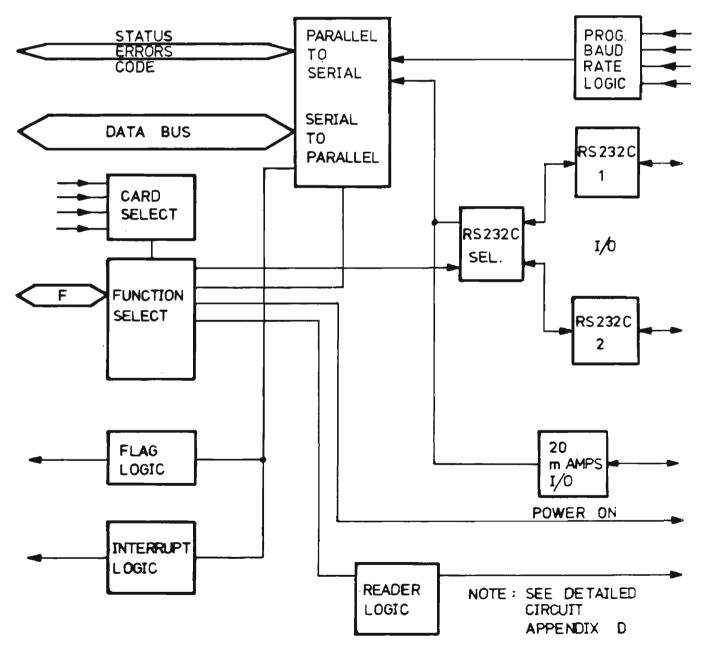

The basic function of the high speed interface cards was to convert the parallel data to serial data and vice versa at a predetermined and flexible speed. In order to meet the requirements of the model, two basic building blocks (a Universal Asychronous Receive and Transmit (UART) chip and a Programmable Baud Rate Chip) were used. These two devices were selected in preference to discrete shift registers in order to minimise the number of components and to standardise the cards as much as possible. The features of the two basic blocks were as follows:

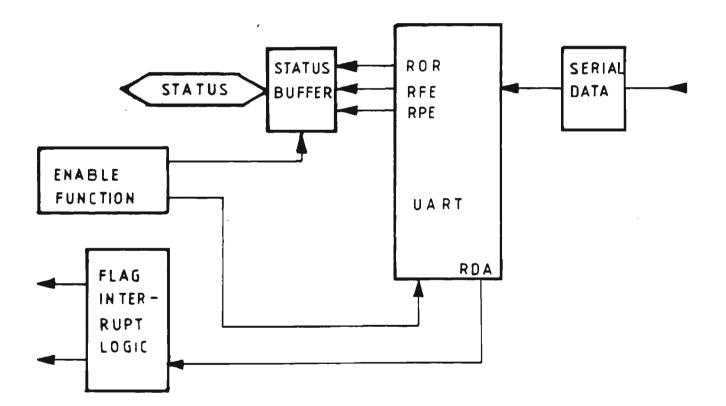

> The UART: This device provided the central processing unit of each sub-system with more time to carry out other tasks while it transferred the data to the peripherals. The peripherals used were 8-bit devices and were within the speed range of the 8-bit UART. Use was made of the inbuilt flags of the UART to interrupt the computer after the data had been received or transmitted in order to transfer the data for processing.

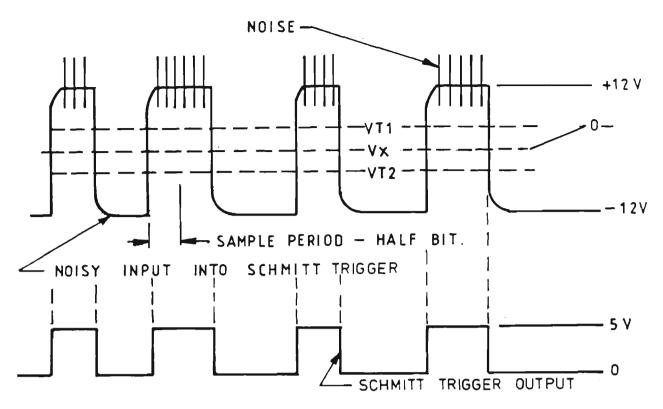

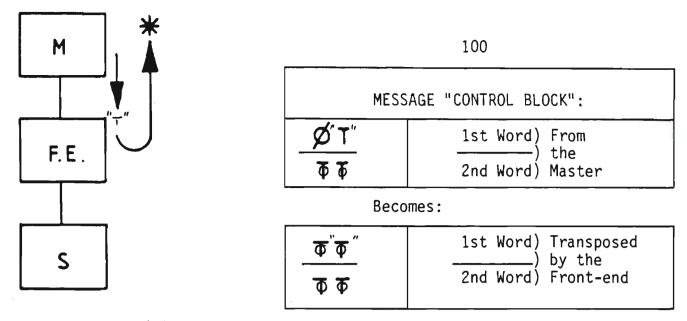

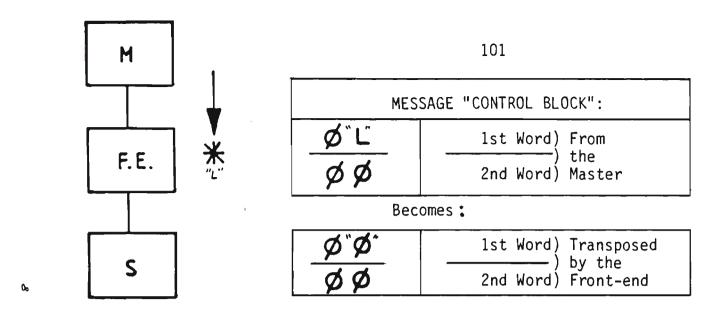

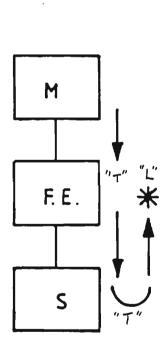

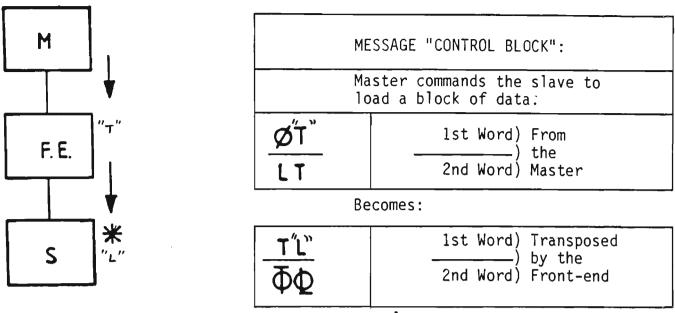

Although the 21MX minicomputer and the PACE microcomputers were able to process 16-bit data, the variable speed and asychronous features of the UART outweighed the disadvantage of processing 8-bit data. In both the 21MX minicomputer and PACE Microcomputer, the least significant 8 bits of the 16-bit data bus were used for the data transfers via the UART interface cards.